Xilinx VC707 User Manual

Evaluation board for the virtex-7 fpga

Hide thumbs

Also See for VC707:

- User manual (116 pages) ,

- Manual (82 pages) ,

- Getting started (24 pages)

Summary of Contents for Xilinx VC707

- Page 1 VC707 Evaluation Board for the Virtex-7 FPGA User Guide UG885 (v1.8) February 20, 2019...

-

Page 2: Please Read: Important Legal Notices

(including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. - Page 3 Memory. Updated the U1 FPGA Pin for F31 and F32 in Table 1-28. In Appendix C, Xilinx Constraints File changed the title of the appendix, updated the description and removed the VC707 Board XDC Listing. Updated Appendix F, Regulatory and Compliance Information. Updated Appendix G, References UG885 (v1.8) February 20, 2019...

- Page 4 VC707 Evaluation Board www.xilinx.com UG885 (v1.8) February 20, 2019...

-

Page 5: Table Of Contents

VC707 Board Features ........ - Page 6 Appendix D: Board Setup Installing VC707 Board in a PC Chassis ........89...

-

Page 7: Chapter 1: Vc707 Evaluation Board Features

VC707 Evaluation Board Features Overview The VC707 evaluation board for the Virtex®-7 FPGA provides a hardware environment for developing and evaluating designs targeting the Virtex-7 XC7VX485T-2FFG1761C FPGA. The VC707 board provides features common to many embedded processing systems, including a DDR3 SODIMM memory, an 8-lane PCI Express®... - Page 8 VC707 Evaluation Board Features Chapter 1: • PCI Express endpoint connectivity • Gen1 8-lane (x8) • Gen2 8-lane (x8) • SFP+ Connector • 10/100/1000 tri-speed Ethernet PHY • USB-to-UART bridge • HDMI™ codec • C bus • C MUX •...

-

Page 9: Electrostatic Discharge Caution

The VC707 board block diagram is shown in Figure 1-1. The VC707 board schematics are available for download from the VC707 Evaluation Kit product page on the Docs & Designs tab at www.xilinx.com/vc707. Electrostatic Discharge Caution ESD can damage electronic components when they are improperly handled, and can Caution! result in total or intermittent failures. - Page 10 DIP Switch SW11 JTAG Interface USB-to-UART Bridge SFP+ Single Cage I 2 C Bus Switch Config and Flash Addr mini-B USB Connector UG885_c1_01_030512 Figure 1-1: VC707 Board Block Diagram www.xilinx.com VC707 Evaluation Board Send Feedback UG885 (v1.8) February 20, 2019...

-

Page 11: Feature Descriptions

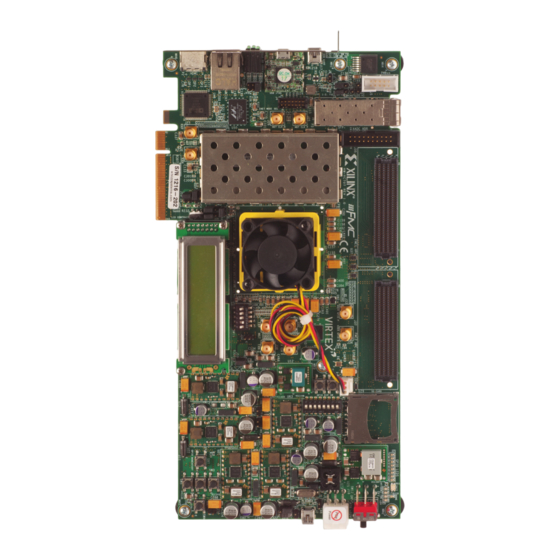

Feature Descriptions Feature Descriptions Figure 1-2 shows the VC707 board. Each numbered feature that is referenced in Figure 1-2 described in the sections that follow. The image in Figure 1-2 is for reference only and might not reflect the current revision of the Note: board. - Page 12 VC707 Evaluation Board Features Chapter 1: Table 1-1: VC707 Board Component Descriptions (Cont’d) Schematic Reference 0381418 Callout Component Description Notes Designator Page Number C programmable user clock LVDS, Silicon Labs SI570BAB0000544DG 156.250 MHz default frequency (back side of board) J31, J32...

-

Page 13: Virtex-7 Xc7Vx485T-2Ffg1761C Fpga

[Ref 1], and 7 Series FPGAs Packaging and Pinout Product Specifications User Guide (UG475) [Ref 14]. To determine the type of FPGA resident on the VC707 board, refer to the Master Answer Record listed in Appendix G: References. FPGA Configuration The VC707 board supports two of the five 7 series FPGA configuration modes: •... - Page 14 There are 17 I/O banks available on the Virtex-7 device. Sixteen I/O banks are available on the VC707 board, bank 31 is not used. The voltages applied to the FPGA I/O banks used by the VC707 board are listed in Table 1-3.

-

Page 15: Ddr3 Memory

Datapath width: 64 bits • Data rate: Up to 1,600 MT/s The VC707 XC7VX485T FPGA memory interface performance is documented in the Virtex-7 T and XT FPGAs Data Sheet: DC and AC Switching Characteristics (DS183) [Ref The DDR3 interface is implemented across I/O banks 37, 38, and 39. Each bank is a 1.5V high-performance bank having a dedicated DCI VRP/N resistor connection. - Page 16 VC707 Evaluation Board Features Chapter 1: Table 1-4: DDR3 Memory Connections to the FPGA (Cont’d) J1 DDR3 Memory FPGA (U1) Pin Net Name I/O Standard Pin Number Pin Name DDR3_BA2 SSTL15 DDR3_D0 SSTL15 DDR3_D1 SSTL15 DDR3_D2 SSTL15 DDR3_D3 SSTL15 DDR3_D4...

- Page 17 SSTL15 DQ53 DDR3_D54 SSTL15 DQ54 DDR3_D55 SSTL15 DQ55 DDR3_D56 SSTL15 DQ56 DDR3_D57 SSTL15 DQ57 DDR3_D58 SSTL15 DQ58 DDR3_D59 SSTL15 DQ59 DDR3_D60 SSTL15 DQ60 DDR3_D61 SSTL15 DQ61 DDR3_D62 SSTL15 DQ62 VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

- Page 18 VC707 Evaluation Board Features Chapter 1: Table 1-4: DDR3 Memory Connections to the FPGA (Cont’d) J1 DDR3 Memory FPGA (U1) Pin Net Name I/O Standard Pin Number Pin Name DDR3_D63 SSTL15 DQ63 DDR3_DM0 SSTL15 DDR3_DM1 SSTL15 DDR3_DM2 SSTL15 DDR3_DM3 SSTL15...

-

Page 19: Linear Bpi Flash Memory

DDR3_CLK1_P DIFF_SSTL15 CK1_P The VC707 DDR3 SODIMM interface adheres to the constraints guidelines in the DDR3 Design Guidelines section of 7 Series FPGAs Memory Interface Solutions User Guide (UG586) [Ref The VC707 DDR3 SODIMM interface is a 40Ω impedance implementation. Other memory... - Page 20 VC707 Evaluation Board Features Chapter 1: Table 1-5: BPI Flash Memory Connections to the FPGA BPI Flash Memory (U3) FPGA (U1) Pin Net Name I/O Standard Pin Number Pin Name AJ28 FLASH_A0 LVCMOS18 AH28 FLASH_A1 LVCMOS18 AG31 FLASH_A2 LVCMOS18 AF30...

- Page 21 The configuration section of 7 Series FPGAs Configuration User Guide (UG470) [Ref 3] provides details on the Master BPI configuration mode. Figure 1-4 shows the connections of the linear BPI Flash memory on the VC707 board. For more details, see the Micron PC28F00AG18FE data sheet [Ref 17]. VC707 Evaluation Board www.xilinx.com...

- Page 22 VC707 Evaluation Board Features Chapter 1: X-Ref Target - Figure 1-4 PC28F00AG18FE 64-Pin BGA (8 x 10 mm) FLASH_A0 FLASH_D0_R FLASH_D1_R FLASH_A1 FLASH_D2_R FLASH_A2 FLASH_D3_R FLASH_A3 FLASH_D4_R FLASH_A4 FLASH_D5_R FLASH_A5 FLASH_D6_R FLASH_A6 FLASH_D7_R FLASH_A7 FLASH_D8_R FLASH_A8 FLASH_A9 FLASH_D9_R FLASH_D10_R FLASH_A10...

-

Page 23: Usb 2.0 Ulpi Transceiver

The VC707 board uses a Standard Microsystems Corporation USB3320 USB 2.0 ULPI Transceiver (U8) to support a USB connection to the host computer. A USB cable is supplied in the VC707 Evaluation Kit (type-A connector to host computer, mini-B connector to VC707 board connector J2). - Page 24 VC707 Evaluation Board Features Chapter 1: The connections between the USB mini-B connector at J2 and the PHY at U8 are listed in Table 1-6. Table 1-6: USB Connector Pin Assignments and Signal Definitions Between J2 and U8 USB Connector...

-

Page 25: Sd Card Interface

[Figure 1-2, callout 5] The VC707 board includes a secure digital input/output (SDIO) interface to provide user-logic access to general purpose nonvolatile SDIO memory cards and peripherals. The SD card slot is designed to support 50 MHz high speed SD cards. -

Page 26: Usb Jtag

[Figure 1-2, callout 6] JTAG configuration is provided through a Digilent onboard USB-to-JTAG configuration logic module (U26) where a host computer accesses the VC707 board JTAG chain through a type-A (host side) to micro-B (VC707 board side) USB cable. www.xilinx.com... - Page 27 UG885_c1_07_021412 Figure 1-7: JTAG Chain Block Diagram When an FMC mezzanine card is attached to the VC707 board it is automatically added to the JTAG chain through electronically controlled single-pole single-throw (SPST) switches U27 and U28. The SPST switches are in a normally closed state and transition to an open state when an FMC mezzanine card is attached.

- Page 28 VC707 Evaluation Board Features Chapter 1: The JTAG circuit details are shown in Figure 1-8. X-Ref Target - Figure 1-8 VCC3V3 VCC3V3 SN74LV541A Voltage Digilent FMC1 HPC Translator USB-JTAG Connector FMC1_HPC_PRSNT_M2C_B Module R95 15Ω PRSNT_L FMC_TDI_BUF R96 15Ω SN74LV541A Voltage R94 15Ω...

-

Page 29: Clock Generation

Feature Descriptions Clock Generation The VC707 board provides five clock sources for the FPGA. Table 1-9 lists the source devices for each clock. Table 1-9: VC707 Board Clock Sources Clock Clock Name Description Source SiT9102 2.5V LVDS 200 MHz Fixed Frequency Oscillator (SiTime). - Page 30 [Figure 1-2, callout 7] The VC707 board has a LVDS 200 MHz oscillator (U51) soldered onto the back side of the board and wired to an FPGA MRCC clock input on bank 38. This 200 MHz signal pair is named SYSCLK_P and SYSCLK_N, which are connected to FPGA U1 pins E19 and E18 respectively.

- Page 31 FPGA U1 pins AJ32 and AK32 respectively. The user-provided 1.8 V differential clock circuit is shown in Figure 1-11. X-Ref Target - Figure 1-11 USER_SMA_CLOCK_P Connector USER_SMA_CLOCK_N Connector UG885_c1_11_020612 Figure 1-11: User SMA Clock Source VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

- Page 32 [Figure 1-2, callout 10] The VC707 board includes a pair of SMA connectors for a GTX clock wired to GTX Quad bank 113. This differential clock has signal names SMA_MGT_REFCLK_P and SMA_REFCLK_N, which are connected to FPGA U1 pins AK8 and AK7 respectively.

-

Page 33: Gtx Transceivers

Quad can be sourced from the Quad above or Quad below the GTX Quad of interest. Seven of the nine GTX Quads are used on the VC707 board, with connectivity as shown here (Quads 111 and 112 are not used): VC707 Evaluation Board www.xilinx.com... - Page 34 VC707 Evaluation Board Features Chapter 1: • Quad 113: • MGTREFCLK0 - SGMII clock • MGTREFCLK1 - SMA clock • Contains 3 GTX transceivers with one each allocated to SMA, SGMII and SFP • Contains 1 unused GTX transceiver •...

- Page 35 FMC1 HPC DP2 GTXE2_CHANNEL_X1Y27 FMC1 HPC DP3 MGTREFCLK0 FMC1 HPC GBT_CLK0 MGTREFCLK1 For more information on the GTX transceivers, see 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476) [Ref VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

-

Page 36: Pci Express Endpoint Connectivity

100Ω differential pair. The 7 series FPGAs GTX transceivers are used for multi-gigabit per second serial interfaces. The XC7VX485T-2FFG1761C FPGA (-2 speed grade) included with the VC707 board supports up to Gen2 x8. The PCIe clock is input from the edge connector. It is AC coupled to the FPGA through the MGTREFCLK1 pins of Quad 115. - Page 37 J49 2, 4, 6 PRSNT#1 J49 Lane Size Select jumper PCIE_WAKE_B AV33 WAKE# Integrated Endpoint block wake signal, not connected on KC705 Board PCIE_PERST_B AV35 PERST Integrated Endpoint block reset signal VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

- Page 38 VC707 Evaluation Board Features Chapter 1: Table 1-13 lists the PCIe edge connector connections for Quad 115. Table 1-13: GTX Quad 115 PCIe Edge Connector Connections PCIe Edge Connector (P1) Quad 115 FPGA (U1) FHG1761 Net Name Pin Name Placement...

- Page 39 For more information refer to 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476) [Ref 7] and 7 Series FPGAs Integrated Block for PCI Express Product Guide for Vivado Design Suite (PG054) [Ref VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

-

Page 40: Sfp/Sfp+ Module Connector

Chapter 1: SFP/SFP+ Module Connector [Figure 1-2, callout 14] The VC707 board contains a small form-factor pluggable (SFP+) connector and cage assembly P3 that accepts SFP or SFP+ modules. Figure 1-16 shows the SFP+ module connector circuitry. X-Ref Target - Figure 1-16... -

Page 41: 10/100/1000 Tri-Speed Ethernet Phy

[Figure 1-2, callout 15] The VC707 board utilizes the Marvell Alaska PHY device (88E1111) U50 for Ethernet communications at 10, 100, or 1000 Mb/s. The board supports SGMII mode only. The PHY connection to a user-provided Ethernet cable is through a Halo HFJ11-1G01E RJ-45 connector (P4) with built-in magnetics. - Page 42 VC707 Evaluation Board Features Chapter 1: Table 1-17: Board Connections for PHY Configuration Pins Bit[2] Bit[1] Bit[0] Connection on Board Definition and Value Definition and Value Definition and Value CFG0 2.5V PHYADR[2] = 1 PHYADR[1] = 1 PHYADR[0] = 1...

-

Page 43: Sgmii Gtx Transceiver Clock Generation

The VC707 board contains a Silicon Labs CP2103GM USB-to-UART bridge device (U44) which allows a connection to a host computer with a USB port. The USB cable is supplied in the VC707 Evaluation Kit (Type-A end to host computer, Type mini-B end to VC707 board connector J17). The CP2103GM is powered by the USB 5V provided by the host PC when the USB cable is plugged into the USB port on the VC707 board. -

Page 44: Hdmi Video Output

VC707 Evaluation Board Features Chapter 1: drivers must be installed on the host PC prior to establishing communications with the VC707 board. The USB Connector Pin Assignments and Signal Definitions between J17 and U44 are listed in Table 1-19. Table 1-19: USB Connector J17 Pin Assignments and Signal Definitions... - Page 45 DSD4 DSD5 DSD_CLK MCLK GND1 GND2 GND3 I2S0 GND4 I2S1 GND5 I2S2 GND6 I2S3 GND7 SCLK GND8 LRCLK GND9 GND10 R_EXT GND11 R433 UG855_c1_18_020612 Figure 1-18: HDMI Codec Circuit VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

- Page 46 VC707 Evaluation Board Features Chapter 1: Table 1-21 lists the connections between the codec and the FPGA. Table 1-21: FPGA to HDMI Codec Connections (ADV7511) ADV7511 (U48) FPGA (U1) Pin Schematic Net Name I/O Standard Pin Number Pin Name AM22...

- Page 47 HDMI_D1_P HDMI_D1_N HDMI_D2_P HDMI_D2_N HDMI_CLK_P HDMI_CLK_N HDMI_DDCSDA HDMI_DDCSCL HDMI_HEAC_P HDMI_HEAC_N HDMI_CRC Information about the ADV7511 is available on the Analog Devices website [Ref 23]. Search for the term ADV7511KSTZ-P. VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

-

Page 48: Lcd Character Display (16 X 2)

VC707 Evaluation Board Features Chapter 1: LCD Character Display (16 x 2) [Figure 1-2, callout 19] A 2-line by 16-character display is provided on the VC707 board (Figure 1-19). X-Ref Target - Figure 1-19 LCD Display (16 x 2) UG885_c1_19_020612 Figure 1-19: LCD Display The character display runs at 5.0V and is connected to the FPGA's 1.8V HP bank 15 through a TI... -

Page 49: I 2 C Bus

Feature Descriptions The VC707 board base board uses a male Samtec MTLW-107-07-G-D-265 2x7 header (J23) with 0.025-inch square posts on 0.100-inch centers for connecting to a Samtec SLW-107-01-L-D female socket on the LCD display panel assembly. The LCD header shown in Figure 1-21. - Page 50 VC707 Evaluation Board Features Chapter 1: The VC707 board I C bus topology is shown in Figure 1-22. X-Ref Target - Figure 1-22 PCA9548 1 2 C 1-to-8 Bus Switch CH0 - USER_CLK_SDL/SCL CH1 - FMC1_HPC_IIC_SDA/SCL FPGA Bank 15 CH2 - FMC2_HPC_IIC_SDA/SCL (2.5V)

-

Page 51: Status Leds

TPS51200 Power Good (U23) User I/O [Figure 1-2, callout - 26] The VC707 board provides the following user and general purpose I/O capabilities: • Eight user LEDs (callout 22) • GPIO_LED_[7-0]: DS9, DS8, DS7, DS6, DS5, DS4, DS3, DS2 •... - Page 52 VC707 Evaluation Board Features Chapter 1: User LEDs Figure 1-23 shows the user LED circuits. X-Ref Target - Figure 1-23 GPIO_LED_0 GPIO_LED_1 GPIO_LED_2 GPIO_LED_3 GPIO_LED_4 GPIO_LED_5 GPIO_LED_6 GPIO_LED_7 R154 R153 R152 R151 R150 R149 R148 R147 49.9Ω 49.9Ω 49.9Ω 49.9Ω...

- Page 53 GPIO SW W GPIO SW C GPIO SW E 4.7kΩ 4.7kΩ 4.7kΩ 0.1 W 0.1 W 0.1 W VCC1V8 GPIO SW S 4.7kΩ 0.1 W UG885_c1_24_012113 Figure 1-25: User Pushbuttons VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

- Page 54 VC707 Evaluation Board Features Chapter 1: GPIO DIP Switch Circuit Figure 1-26 shows the GPIO DIP switch circuit. X-Ref Target - Figure 1-26 VADJ GPIO_DIP_SW0 GPIO_DIP_SW1 GPIO_DIP_SW2 GPIO_DIP_SW3 GPIO_DIP_SW4 GPIO_DIP_SW5 GPIO_DIP_SW6 GPIO_DIP_SW7 SDA08H1SBD 4.7kΩ 4.7kΩ 4.7kΩ 4.7kΩ 0.1 W 0.1 W 0.1 W...

- Page 55 LVCMOS18 DS8.2 AU39 GPIO_LED_7 LVCMOS18 DS9.2 CPU Reset Pushbutton Switch AV40 CPU_RESET LVCMOS18 SW8.3 Directional Pushbutton Switches AR40 GPIO_SW_N LVCMOS18 SW3.3 AU38 GPIO_SW_E LVCMOS18 SW4.3 AP40 GPIO_SW_S LVCMOS18 SW5.3 VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

-

Page 56: Switches

[Figure 1-2, callout 27] The VC707 board power switch is SW12. Sliding the switch actuator from the Off to On position applies 12V power from J18, a 6-pin mini-fit connector. Green LED DS16 illuminates when the VC707 board power is on. See Power Management for details on the onboard power system. - Page 57 Figure 1-29 for powering the VC707 board from the ATX power supply 4-pin peripheral connector. The Xilinx part number for this cable is 2600304, and is equivalent to Sourcegate Technologies part number AZCBL-WH-1109-RA4. For information on ordering this cable, see [Ref 27].

- Page 58 VC707 Evaluation Board Features Chapter 1: X-Ref Target - Figure 1-31 VCC1V9 4.7kΩ 0.1 W FPGA_PROG_B UG885_c1_28_030512 Figure 1-31: FPGA_PROG_B Pushbutton SW9 Configuration Mode and Upper Linear Flash Address Switch (SW11) [Figure 1-2, callout 29] FPGA Configuration Mode: DIP switch SW11 positions 3, 4, and 5 control which configuration mode is used at power-up or when the PROG pushbutton is pressed.

-

Page 59: Vita 57.1 Fmc1 Hpc Connector (Partially Populated)

2 GTX clocks • 4 differential clocks • 159 ground and 15 power connections The VC707 board FMC1 HPC connector J35 implements a subset of the maximum signal and clock connectivity capabilities: • 80 differential user-defined pairs • 34 LA pairs (LA00-LA33) •... - Page 60 • 4 differential clocks • 159 ground and 15 power connections The VC707 board FMC2 HPC connector J37 implements a subset of the maximum signal and clock connectivity capabilities: • 58 differential user-defined pairs (as shipped with the Virtex-7 XC7VX485T-2FFG1761C FPGA installed on the VC707 board, the FMC2 HB00-HB21 bus connections are not supported.

- Page 61 FMC1_HPC_DP1_M2C_N FMC1_HPC_DP2_M2C_P FMC1_HPC_DP2_M2C_N FMC1_HPC_DP3_M2C_P FMC1_HPC_DP3_M2C_N FMC1_HPC_DP7_M2C_P FMC1_HPC_DP4_M2C_P FMC1_HPC_DP7_M2C_N FMC1_HPC_DP4_M2C_N FMC1_HPC_DP6_M2C_P FMC1_HPC_DP5_M2C_P FMC1_HPC_DP6_M2C_N FMC1_HPC_DP5_M2C_N FMC1_HPC_GBTCLK1_M2C_P FMC1_HPC_DP1_C2M_P FMC1_HPC_GBTCLK1_M2C_N FMC1_HPC_DP1_C2M_N FMC1_HPC_DP2_C2M_P FMC1_HPC_DP2_C2M_N FMC1_HPC_DP3_C2M_P FMC1_HPC_DP3_C2M_N FMC1_HPC_DP7_C2M_P FMC1_HPC_DP4_C2M_P FMC1_HPC_DP7_C2M_N FMC1_HPC_DP4_C2M_N FMC1_HPC_DP6_C2M_P FMC1_HPC_DP5_C2M_P FMC1_HPC_DP6_C2M_N FMC1_HPC_DP5_C2M_N VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

- Page 62 VC707 Evaluation Board Features Chapter 1: Table 1-27: J35 VITA 57.1 FMC HPC Connections (Cont’d) FMC 1 U1 FPGA FMC 1 Schematic Net Name Standard Schematic Net Name FPGA Standard FMC1_HPC_DP0_C2M_P PWRCTL1_VCC4B_PG AL32 FMC1_HPC_DP0_C2M_N FMC1_HPC_GBTCLK0_M2C_P FMC1_HPC_DP0_M2C_P FMC1_HPC_GBTCLK0_M2C_N FMC1_HPC_DP0_M2C_N FMC1_HPC_LA01_CC_P LVCMOS18...

- Page 63 LVCMOS18 FMC1_HPC_HB13_P LVCMOS18 FMC1_HPC_HB08_N LVCMOS18 FMC1_HPC_HB13_N LVCMOS18 FMC1_HPC_HB12_P LVCMOS18 FMC1_HPC_HB19_P LVCMOS18 FMC1_HPC_HB12_N LVCMOS18 FMC1_HPC_HB19_N LVCMOS18 FMC1_HPC_HB16_P LVCMOS18 FMC1_HPC_HB21_P LVCMOS18 FMC1_HPC_HB16_N LVCMOS18 FMC1_HPC_HB21_N LVCMOS18 FMC1_HPC_HB20_P LVCMOS18 VADJ FMC1_HPC_HB20_N LVCMOS18 VADJ VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

- Page 64 VC707 Evaluation Board Features Chapter 1: Table 1-27: J35 VITA 57.1 FMC HPC Connections (Cont’d) FMC 1 U1 FPGA FMC 1 Schematic Net Name Standard Schematic Net Name FPGA Standard FMC1_HPC_CLK1_M2C_P LVCMOS18 FMC1_HPC_CLK1_M2C_N LVCMOS18 FMC1_HPC_PRSNT_M2C_B LVCMOS18 AM31 FMC1_HPC_LA00_CC_P LVCMOS18 FMC1_HPC_CLK0_M2C_P...

- Page 65 LVCMOS18 FMC1_HPC_HB18_P LVCMOS18 FMC1_HPC_HB14_N LVCMOS18 FMC1_HPC_HB18_N LVCMOS18 FMC1_HPC_HB17_CC_P LVCMOS18 FMC1_HPC_HB17_CC_N LVCMOS18 FMC1_VIO_B_M2C BANK 36 FMC1_VIO_B_M2C BANK 36 VCCO VCCO Notes: 1. No I/O standards are associated with MGT connections. VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

- Page 66 FMC2 HPC J37 connector and the FPGA U1. The FMC2 HPC HB00-HB21 pair connections are not available with the Note: XC7VX485T-2FFG1761C FPGA installed on the VC707. Refer to the Virtex-7 FPGA VC707 Evaluation Kit Master Answer Record in Appendix References for more information.

- Page 67 FMC2_HPC_LA26_P LVCMOS18 GA0 = 0 = GND FMC2_HPC_LA26_N LVCMOS18 VCC12_P FMC2_HPC_TCK_BUF U19.13 VCC12_P FMC1_TDO_FMC2_TDI U27.2 VCC3V3 FMC2_TDO_FPGA_TDI U46.3 VCC3V3 FMC2_HPC_TMS_BUF U19.16 GA1 = 0 = GND VCC3V3 VCC3V3 VCC3V3 VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

- Page 68 VC707 Evaluation Board Features Chapter 1: Table 1-28: J37 VITA 57.1 FMC 2 HPC Connections (Cont’d) FMC 2 U1 FPGA FMC 2 U1 FPGA Schematic Net Name Schematic Net Name Standard Standard FMC2_HPC_HA01_CC_P AD32 FMC2_HPC_PG_M2C AF29 LVCMOS18 LVCMOS18 FMC2_HPC_HA01_CC_N AD33...

- Page 69 FMC2_HPC_LA24_P LVCMOS18 LVCMOS18 FMC2_HPC_LA29_N FMC2_HPC_LA24_N LVCMOS18 LVCMOS18 FMC2_HPC_LA31_P FMC2_HPC_LA28_P LVCMOS18 LVCMOS18 FMC2_HPC_LA31_N FMC2_HPC_LA28_N LVCMOS18 LVCMOS18 FMC2_HPC_LA33_P FMC2_HPC_LA30_P LVCMOS18 LVCMOS18 FMC2_HPC_LA33_N FMC2_HPC_LA30_N LVCMOS18 LVCMOS18 VADJ FMC2_HPC_LA32_P LVCMOS18 FMC2_HPC_LA32_N LVCMOS18 VADJ VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

- Page 70 VC707 Evaluation Board Features Chapter 1: Table 1-28: J37 VITA 57.1 FMC 2 HPC Connections (Cont’d) FMC 2 U1 FPGA FMC 2 U1 FPGA Schematic Net Name Schematic Net Name Standard Standard FMC2_HPC_HA03_P AA29 LVCMOS18 FMC2_HPC_HA03_N AA30 FMC2_HPC_HA02_P AC30 LVCMOS18...

-

Page 71: Power Management

Feature Descriptions Power Management The VC707 board power distribution diagram is shown in Figure 1-33. The PCB layout and power system meet the recommended criteria described in 7 Series FPGAs PCB Design Guide (UG483) [Ref 10]. X-Ref Target - Figure 1-33... - Page 72 VC707 Evaluation Board Features Chapter 1: The VC707 board uses power regulators and PMBus compliant digital PWM system controllers from Texas Instruments to supply the core and auxiliary voltages listed in Table 1-29. Table 1-29: Onboard Power System Devices Reference...

- Page 73 26]. FMC_VADJ Voltage Control The FMC_VADJ rail is set to 1.8V. When the VC707 board is powered on, the state of the FMC_VADJ_ON_B signal wired to header J51 is sampled by the TI UCD9248 controller U42. If a jumper is installed on J51 signal FMC_VADJ_ON_B is held low, and the TI controller U42 energizes the FMC_VADJ rail at power on.

- Page 74 VC707 Evaluation Board Features Chapter 1: Table 1-30 defines the voltage and current values for each power rail controlled by the UCD9248 PMBus controller at address 52 (U42). Table 1-30: Power Rail Specifications for UCD9248 PMBus Controller at Address 52...

- Page 75 PCIe Form Factor Board TI Power System Cooling If the power modules on the VC707 board are operating at moderate to high current levels (due to a customer design), the modules can generate substantial heat, which can cause them to shut down without warning.

-

Page 76: Xadc Analog-To-Digital Converter

UG885_c1_31_030512 Figure 1-34: XADC Block Diagram The VC707 board supports both the internal FPGA sensor measurements and the external measurement capabilities of the XADC. Internal measurements of the die temperature, VCCINT, VCCAUX, and VCCBRAM are available. The VC707 board VCCINT and VCCBRAM are provided by a common 1.0 V supply. - Page 77 Digital I/O. These pins should come from the same bank. These I/Os should not be XADC_GPIO_3, 2, 1, 0 19, 20, 17, 18 shared with other functions because they are required to support 3-state operation. VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

-

Page 78: Configuration Options

VC707 Evaluation Board Features Chapter 1: Configuration Options The FPGA on the VC707 board can be configured by the following methods: • Master BPI (uses the Linear BPI Flash). • JTAG (uses the USB-to-JTAG Bridge or Download cable). See USB JTAG... - Page 79 FLASH_A[25:0] A[26:01] A[23:16] A[15:00] D[15:00] D[15:00] Bank 14 (VCCO = 1.8V) CE_B FCS_B RDWR_B WAIT (VCC, VCCQ, 1.8V) Oscillator EMCCLK 80 MHz UG885_c1_34_030512 Figure 1-37: VC707 Board Configuration Circuit VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

- Page 80 VC707 Evaluation Board Features Chapter 1: www.xilinx.com VC707 Evaluation Board Send Feedback UG885 (v1.8) February 20, 2019...

-

Page 81: Appendix A: Default Switch And Jumper Settings

2 3 4 5 6 7 8 OFF Position = 0 UG885_aB_01_020612 Figure A-1: SW2 Default Settings Table A-1: SW2 Default Switch Settings Position Function Default GPIO_DIP_SW0 GPIO_DIP_SW1 GPIO_DIP_SW2 GPIO_DIP_SW3 GPIO_DIP_SW4 GPIO_DIP_SW5 GPIO_DIP_SW6 GPIO_DIP_SW7 VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019... -

Page 82: Configuration Dip Switch Sw11

SFP RX Rate: 1-2 = Full BW Rate, 2-3 = Low BW Rate 1–2 SFP TX Rate: 1-2 = Full BW Rate, 2-3 = Low BW Rate 1–2 XADC external 1.2V or internal VREFP selector 1–2 www.xilinx.com VC707 Evaluation Board Send Feedback UG885 (v1.8) February 20, 2019... - Page 83 TI Controller U64 Addr 54 Reset jumper None FMC_VADJ_ON_B jumper 1–2 XADC VCC5V0-to-XADC_VCC5V0 jumper 1–2 XADC REF3012 U35 V Select 1–2 X-Ref Target - Figure A-3 UG885_aA_03_081814 Figure A-3: VC707 Board Jumper Header Locations VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019...

- Page 84 Default Switch and Jumper Settings Appendix A: www.xilinx.com VC707 Evaluation Board Send Feedback UG885 (v1.8) February 20, 2019...

-

Page 85: Appendix B: Vita 57.1 Fmc Connector Pinouts

LA33_N HB20_P HB21_N 12P0V DP6_C2M_N HB17_N_CC LA32_N HB20_N 3P3V DP5_C2M_P VIO_B_M2C VADJ VADJ 3P3V DP5_C2M_N VIO_B_M2C VADJ VADJ 3P3V RES0 UG885_aC_01_020612 Figure B-1: FMC1 and FMC2 HPC Connector Pinout VC707 Evaluation Board www.xilinx.com Send Feedback UG885 (v1.8) February 20, 2019... - Page 86 VITA 57.1 FMC Connector Pinouts Appendix B: www.xilinx.com VC707 Evaluation Board Send Feedback UG885 (v1.8) February 20, 2019...

-

Page 87: Appendix C: Xilinx Constraints File

The VC707 board Xilinx design constraints (XDC) file template provides for designs targeting the VC707 board. Net names in the constraints correlate with net names on the latest VC707 board schematic. Users must identify the appropriate pins and replace the net names listed here with net names in the user RTL. - Page 88 Xilinx Constraints File Appendix C: www.xilinx.com VC707 Evaluation Board Send Feedback UG885 (v1.8) February 20, 2019...

-

Page 89: Appendix D: Board Setup

Installation of the VC707 board inside a computer chassis is required when developing or testing PCI Express functionality. When the VC707 board is used inside a computer chassis (that is, plugged in to the PCIe® slot), power is provided from the ATX power supply 4-pin peripheral connector through the ATX adapter... - Page 90 Board Setup Appendix D: www.xilinx.com VC707 Evaluation Board Send Feedback UG885 (v1.8) February 20, 2019...

-

Page 91: Appendix E: Board Specifications

Board Specifications Dimensions Height: 5.5 inch (14.0 cm) Thickness (±5%): 0.062 inch (0.1575 cm) Length: 10.5 inch (26.7 cm) The VC707 board height exceeds the standard 4.376 inch (11.15 cm) height of a PCI Express Note: card. Environmental Temperature Operating: 0°C to +45°C Storage: –25°C to +60°C... - Page 92 Board Specifications Appendix E: www.xilinx.com VC707 Evaluation Board Send Feedback UG885 (v1.8) February 20, 2019...

-

Page 93: Appendix F: Regulatory And Compliance Information

This product is designed and tested to conform to the European Union directives and standards described in this section. See the Virtex-7 FPGA VC707 Evaluation Kit Master Answer Record (AR 45382) for information on the CE requirements for the PC test environment. -

Page 94: Markings

Xilinx has met its national obligations to the EU WEEE Directive by registering in those countries to which Xilinx is an importer. Xilinx has also elected to join WEEE Compliance Schemes in some countries to help manage customer returns at end-of-life. -

Page 95: Appendix G: Additional Resources

Topics include design assistance, advisories, and troubleshooting tips. References The most up to date information related to the VC707 board and its documentation is available on these websites: Virtex-7 FPGA VC707 Evaluation Kit... - Page 96 Analog Devices (ADP123) 27. The Xilinx ATX cable part number 2600304 is manufactured by Sourcegate Technologies and is equivalent to the Sourcegate Technologies part number AZCBL-WH-11009. Sourcegate only manufactures the latest revision, which is currently A4. To order, contact Aries Ang, aries.ang@sourcegate.net, +65 6483 2878 for price and availability.

Need help?

Do you have a question about the VC707 and is the answer not in the manual?

Questions and answers