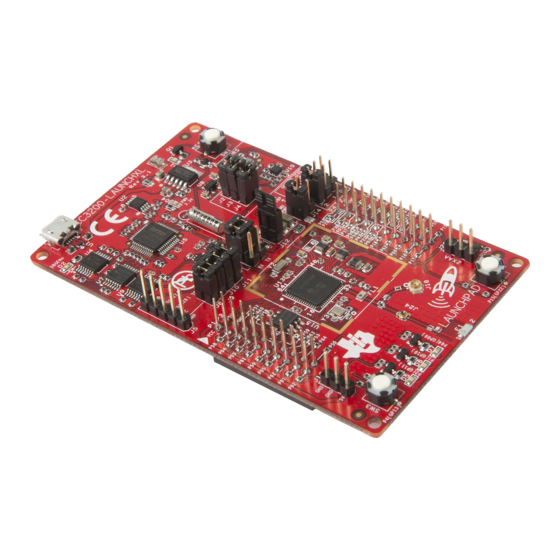

Texas Instruments CC3200 Technical Reference Manual

Simplelink wi-fi and internet-of things

solution, a single chip wireless mcu

Hide thumbs

Also See for CC3200:

- Programmer's manual (73 pages) ,

- User manual (29 pages) ,

- Manual (72 pages)

Subscribe to Our Youtube Channel

Summary of Contents for Texas Instruments CC3200

- Page 1 CC3200 SimpleLink Wi-Fi and Internet-of- Things Solution, a Single Chip Wireless MCU Technical Reference Manual Literature Number: SWRU367D June 2014 – Revised May 2018...

-

Page 2: Table Of Contents

Overview ..................... Functional Description ..................3.2.1 System Timer (SysTick) ..............3.2.2 Nested Vectored Interrupt Controller (NVIC) ..................3.2.3 System Control Block (SCB) Contents SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 3 7.2.6 Command Sequence Flow Charts ................. 7.2.7 Initialization and Configuration ......................Register Map ..................... 7.3.1 I2C Registers ..................SPI (Serial Peripheral Interface) SWRU367D – June 2014 – Revised May 2018 Contents Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 4 SD Host Features ......................11.3 1-Bit SD Interface ................11.3.1 Clock and Reset Management ............... 11.4 Initialization and Configuration Using Peripheral APIs Contents SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 5 14.4.1 Camera Core Reset ................14.4.2 Enable the Picture Acquisition ................14.4.3 Disable the Picture Acquisition ......................14.5 Interrupt Handling ................14.5.1 FIFO_OF_IRQ (FIFO overflow) SWRU367D – June 2014 – Revised May 2018 Contents Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 6 16.8.3 Control Architecture ................... 16.8.4 CC3200 Pin-mux Examples ....................16.8.5 Wake on Pad ....................16.8.6 Sense on Power ................... Software Development Kit Examples Contents SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 7: Contents

B.1.6 DMA_RIS Register (offset = A4h) [reset = 0h] ............B.1.7 GPTTRIGSEL Register (offset = B0h) [reset = 0h] ........................Revision History SWRU367D – June 2014 – Revised May 2018 Contents Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 8 Cortex-M4 Register Set ........................ 2-4. Data Storage ........................ 2-5. Vector Table ....................2-6. Exception Stack Frame ..............2-7. Power Management Architecture in CC3200 SoC ......................3-1. ACTLR Register ......................3-2. STCTRL Register ...................... 3-3. STRELOAD Register ....................3-4. STCURRENT Register ....................

- Page 9 7-6. Data Validity During Bit Transfer on the I2C Bus ....................7-7. Master Single TRANSMIT ....................7-8. Master Single RECEIVE SWRU367D – June 2014 – Revised May 2018 List of Figures Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 10 8-16. Flow Chart - FIFO Mode Common Sequence (Master) ........8-17. Flow Chart - FIFO Mode Transmit and Receive with Word Count (Master) List of Figures SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 11 10-9. WatchDog Flow Chart ................10-10. System WatchDog Recovery Sequence ................11-1. SDHost Controller Interface Block Diagram ....................11-2. MMCHS_CSRE Register SWRU367D – June 2014 – Revised May 2018 List of Figures Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 12 11-17. MMCHS_ISE Register ........................ 12-1. I2S Protocol ......................12-2. MCASP Module ......................12-3. Logical Clock Path ................13-1. Architecture of the ADC Module in CC3200 ....................13-2. Operation of the ADC ..................... 13-3. ADC_CTRL Register ................... 13-4. ADC_CH0_IRQ_EN Register ...................

- Page 13 14-15. CC_CTRL_XCLK Register ....................14-16. CC_FIFODATA Register ............ 15-1. Power Management Unit Supports Two Supply Configurations ......................15-2. Sleep Modes ..............15-3. Power Management Control Architecture in CC3200 ....................15-4. CAMCLKCFG Register ....................15-5. CAMCLKEN Register ....................15-6. CAMSWRST Register ....................

- Page 14 16-1. Board Configuration to Use Pins 45 and 52 as Digital Signals ............. 16-2. Board Configuration to Use Pins 45 and 52 as Digital Signals ............. 16-3. I/O Pad Data and Control Path Architecture in CC3200 ..................16-4. Wake on Pad for Hibernate Mode .......................

- Page 15 DMA_SRCENDP Register Field Descriptions ................. 4-7. DMA_DSTENDP Register Field Descriptions ................4-8. DMA_CHCTL Register Field Descriptions ............4-9. DMA_(OFFSET_FROM_DMA_BASE_ADDRESS) Registers SWRU367D – June 2014 – Revised May 2018 List of Tables Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 16 UARTLCRH Register Field Descriptions ................. 6-10. UARTCTL Register Field Descriptions ................6-11. UARTIFLS Register Field Descriptions ................... 6-12. UARTIM Register Field Descriptions List of Tables SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 17 8-12. SPI_CHCONF Register Field Descriptions ................8-13. SPI_CHSTAT Register Field Descriptions ................8-14. SPI_CHCTRL Register Field Descriptions ..................8-15. SPI_TX Register Field Descriptions SWRU367D – June 2014 – Revised May 2018 List of Tables Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 18 11-6. MMCHS_CON Register Field Descriptions ................11-7. MMCHS_BLK Register Field Descriptions ................11-8. MMCHS_ARG Register Field Descriptions ................11-9. MMCHS_CMD Register Field Descriptions List of Tables SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 19 14-8. CC_CTRL Register Field Descriptions ................. 14-9. CC_CTRL_DMA Register Field Descriptions ................ 14-10. CC_CTRL_XCLK Register Field Descriptions ................14-11. CC_FIFODATA Register Field Descriptions SWRU367D – June 2014 – Revised May 2018 List of Tables Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 20 15-46. TURBOREQ Register Field Descriptions ................ 15-47. DSLPWAKECFG Register Field Descriptions ................15-48. DSLPTIMRCFG Register Field Descriptions ................15-49. SLPWAKEEN Register Field Descriptions List of Tables SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 21 DMA_ICR Register Field Descriptions ................. B-6. DMA_MIS Register Field Descriptions ................. B-7. DMA_RIS Register Field Descriptions ................B-8. GPTTRIGSEL Register Field Descriptions SWRU367D – June 2014 – Revised May 2018 List of Tables Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 22: Architecture Overview

SWRU367D – June 2014 – Revised May 2018 Architecture Overview ........................... Topic Page ....................... Introduction ..................Architecture Overview ................... Functional Overview Architecture Overview SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 23: Introduction

Introduction Created for the Internet of Things (IoT), the SimpleLink CC3200 device is a wireless MCU that integrates a high-performance ARM Cortex-M4 MCU, allowing customers to develop an entire application with a single IC. With on-chip Wi-Fi, Internet, and robust security protocols, no prior Wi-Fi experience is required for faster development. -

Page 24: Architecture Overview

Architecture Overview www.ti.com Architecture Overview The building blocks of CC3200 system-on-chip are shown in Figure 1-1 Figure 1-1. CC3200 MCU and WIFI System-on-Chip Architecture Overview SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 25: Functional Overview

Functional Overview www.ti.com Functional Overview The following sections provide an overview of the main components of the CC3200 system on chip (SoC) from a microcontroller point of view. 1.3.1 Processor Core 1.3.1.1 ARM Cortex M4 Processor Core The CC3200 application MCU subsystem is built around an ARM Cortex-M4 processor core, which provides outstanding computational performance and exceptional system response to interrupts at low power consumption while optimizing memory footprint –... -

Page 26: 1.3.2 Memory

1.3.1.3 Nested Vector Interrupt Controller (NVIC) CC3200 includes the ARM NVIC. The NVIC and Cortex-M3 prioritize and handle all exceptions in handler mode. The processor state is automatically stored to the stack on an exception and automatically restored from the stack at the end of the interrupt service routine (ISR). The interrupt vector is fetched in parallel to the state saving, thus enabling efficient interrupt entry. -

Page 27: Micro Direct Memory Access Controller (Μdma)

Functional Overview www.ti.com The CC3200 DriverLib is a software library that controls on-chip peripherals. The library performs both peripheral initialization and control functions, with a choice of polled or interrupt-driven peripheral support. The ROM DriverLib provides a rich set of drivers for peripheral and chip. It is aimed at reducing application development time and improving solution robustness. -

Page 28: Watch Dog Timer (Wdt)

1.3.5 Watch Dog Timer (WDT) The watchdog timer in the CC3200 restarts the system when it gets stuck due to an error and does not respond as expected. The watchdog timer can be configured to generate an interrupt to the microcontroller on its first time-out, and to generate a reset signal on its second time-out. -

Page 29: Inter-Integrated Circuit Interface (I2C)

SDA and a serial clock line SCL). The I2C bus interfaces to a wide variety of external I2C devices such as sensors, serial memory, control ports of image sensors, and audio codecs. Multiple slave devices can be connected to the same I2C bus. The CC3200 microcontroller includes one I2C module with the following features: •... -

Page 30: General Purpose Input / Output (Gpio)

1.3.10 General Purpose Input / Output (GPIO) All digital pins of the CC3200 device and some of the analog pins can be used as a general-purpose input/output (GPIO). The GPIOs are grouped as 4 instance GPIO modules, each 8-bit. Supported features include: •... -

Page 31: 1.3.15 Hardware Cryptography Accelerator

1.3.15 Hardware Cryptography Accelerator The secure variant of the CC3200 includes a suite of high-throughput, state-of-the-art hardware accelerators for fast computation of ciphers (AES, DES, 3-DES), hashing (SHA, MD5), and CRC algorithms by the application. It is also referred as the data hashing and transform engine (DTHE). Further details about the hardware cryptography accelerator will be addressed in the revision of this manual. -

Page 32: 1.3.17 Simplelink Subsystem

The SimpleLink subsystem provides fast, secured WLAN and Internet connections with 256-bit encryption. The CC3200 device supports station, AP, and Wi-Fi Direct modes. The device also supports WPA2 personal and enterprise security and WPS 2.0. The Wi-Fi network processor includes an embedded IPv4 TCP/IP stack. -

Page 33: Cortex-M4 Processor

Chapter 2 SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Processor ........................... Topic Page ......................Overview ..................Functional Description SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Processor Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 34: Overview

• Low-power consumption with multiple sleep modes The ARM Cortex-M4 application processor core in the CC3200 does not include the floating point unit and memory protection unit (FPU and MPU). This chapter provides information on the implementation of the Cortex-M4 application processor in the CC3200, including the programming model, the memory model, the exception model, fault handling, and power management. -

Page 35: 2.1.2 System-Level Interface

See the ARM Debug Interface V5 Architecture Specification for details on SWJ-DP. The 4-bit trace interface from embedded trace macrocell (ETM) is not supported in the CC3200 due to pin limitations. Instead, the processor integrates an instrumentation trace macrocell (ITM) alongside data watchpoints and a profiling unit. -

Page 36: Trace Port Interface Unit (Tpiu)

– Limited access to the MSR and MRS instructions, and no use of the CPS instruction – No access to the system timer, NVIC, or system control block Cortex-M4 Processor SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 37: Register Description

The core registers are not memory-mapped and are accessed by register name, so the base address is n/a (not applicable) and there is no offset. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Processor Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 38: Cortex-M4 Register Set

Program Status Register PRIMASK 0x0000.0000 Priority Mask Register FAULTMASK 0x0000.0000 Fault Mask Register BASEPRI 0x0000.0000 Base Priority Mask Register CONTROL 0x0000.0000 Control Register Cortex-M4 Processor SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 39 Attempts to write the EPSR using the MSR instruction in application software are always ignored. Fault handlers can examine the EPSR value in the stacked PSR to determine the operation that faulted. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Processor Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 40: Psr Register Combinations

ARM Cortex-M4 Devices Generic User Guide (ARM DUI 0553A), or perform an exception return to thread mode with the appropriate EXC_RETURN value. Cortex-M4 Processor SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 41: Memory Model

0553A). 2.2.2.1.3 Exceptions and Interrupts The Cortex-M4 application processor in the CC3200 supports interrupts and system exceptions. The processor and the nested vectored interrupt controller (NVIC) prioritize and handle all exceptions. An exception changes the normal flow of software control. The processor uses handler mode to handle all exceptions except for reset. -

Page 42: Sram Memory Bit-Banding Regions

This allows bit-band accesses to match the access requirements of the underlying peripheral. The CC3200 family of Wi-Fi microcontrollers support up to 256 Kbyte of on-chip SRAM for code and data. The SRAM starts from address 0x2000 0000. -

Page 43: Data Storage

• The word instructions LDREX and STREX • The halfword instructions LDREXH and STREXH • The byte instructions LDREXB and STREXB SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Processor Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 44: Exception Model

0553A). 2.2.4 Exception Model The ARM Cortex-M4 application processor in the CC3200 and the nested vectored interrupt controller (NVIC) prioritize and handle all exceptions in handler mode. The processor state is automatically stored to the stack on an exception, and automatically restored from the stack at the end of the interrupt service routine (ISR). - Page 45 NMI is permanently enabled and has a fixed priority of –2. NMIs cannot be masked or prevented from activation by any other exception or preempted by any exception other than reset. NMI in the CC3200 is reserved for the internal system, and is not available for application usage. •...

-

Page 46: Exception Types

In the system, peripherals use interrupts to communicate with the processor. Table 2-5 lists the interrupts on the CC3200 application processor For an asynchronous exception, other than reset, the processor can execute another instruction between when the exception is triggered and when the processor enters the exception handler. - Page 47 Functional Description www.ti.com Table 2-7. CC3200 Application Processor Interrupts (continued) Interrupt Number (Bit in Interrupt Vector Adderess or Offset Description Type Registers) 0x0000.0084 ADC Channel-3 0x0000.0088 0x0000.008C 16/32-Bit Timer A0A 0x0000.0090 16/32-Bit Timer A0B 0x0000.0094 16/32-Bit Timer A1A 0x0000.0098 16/32-Bit Timer A1B 0x0000.009C...

-

Page 48: Vector Table

0. NOTE: Configurable priority values for the CC3200 implementation are in the range 0-7. This means that the reset, hard fault, and NMI exceptions (NMI is reserved for use by the system) with fixed negative priority values always have higher priority than any other exception. - Page 49 Figure 2-6 shows the Cortex-M4 stack frame layout, which is similar to that of ARMv7-M implementations without an FPU. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Processor Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 50: Fault Handling

Default memory mismatch on Memory management fault Memory Management Fault MSTKE exception stacking Status (MFAULTSTAT) Occurs on an access to an XN region. Cortex-M4 Processor SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 51 NOTE: Only reset and NMI can preempt the fixed-priority hard fault. A hard fault can preempt any exception other than reset, NMI, or another hard fault. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Processor Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 52: Power Management

NMI occurs, or it is halted by a debugger. 2.2.6 Power Management The CC3200 Wi-Fi microcontroller is a multi-processor system-on-chip. An advanced power management scheme has been implemented at chip level that delivers the best-in-class energy efficiency across a wide class of application profiles, while handling the asynchronous sleep-wake requirements of multiple high performance processors and Wi-Fi radio subsystems. -

Page 53: Power Management Architecture In Cc3200 Soc

Functional Description www.ti.com Figure 2-7 shows the architecture of the CC3200 SoC level power management, especially from the application point of view. Figure 2-7. Power Management Architecture in CC3200 SoC The Cortex-M4 processor implementation inside the CC3200 multiprocessor SoC has a few differences when compared to a discrete MCU. -

Page 54: Instruction Set Summary

RUN (or ACTIVE) state should then be minimized. The dedicated Cortex-M4 application processor in CC3200 is particularly suited for this mode of operation due to its advanced power management, DMA, zero wait state multi-layer AHB interconnect, fast execution and retention over the entire range of zero- wait state SRAM. - Page 55 Saturating add and subtract with exchange QDADD {Rd,} Rn, Rm Saturating double and add QDSUB {Rd,} Rn, Rm Saturating double and subtract SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Processor Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 56 SMMUL, SMMULR {Rd,} Rn, Rm Signed most significant word multiply SMUAD SMUADX {Rd,} Rn, Rm Signed dual multiply add Cortex-M4 Processor SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 57 Unsigned add and subtract with exchange UHADD16 {Rd,} Rn, Rm Unsigned halving add 16 UHADD8 {Rd,} Rn, Rm Unsigned halving add 8 SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Processor Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 58 {Rd,} Rm, {,ROR #n} Unsigned Extend Byte 16 UXTH {Rd,} Rm, {,ROR #n} Zero extend a Halfword Wait for event Wait for interrupt Cortex-M4 Processor SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 59: Cortex-M4 Peripherals

SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals ........................... Topic Page ......................Overview ..................Functional Description ..................... Register Map SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 60: Overview

Overview www.ti.com Overview This chapter provides information on the CC3200 implementation of the Cortex-M4 application processor in CC3200 peripherals, including: • SysTick (see Section 3.2.1) – Provides a simple, 24-bit clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism. •... -

Page 61: Nested Vectored Interrupt Controller (Nvic)

In this case, when the processor returns from the ISR the state of the interrupt changes to pending, which might cause the processor to SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 62: System Control Block (Scb)

0x184 DIS1 0x0000.0000 Interrupt 32-63 Clear Enable 0x188 DIS2 0x0000.0000 Interrupt 64-95 Clear Enable 0x18C DIS3 0x0000.0000 Interrupt 96-127 Clear Enable Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 63 Interrupt 20-23 Priority 0x418 PRI6 0x0000.0000 Interrupt 24-27 Priority 0x41C PRI7 0x0000.0000 Interrupt 28-31 Priority 0x420 PRI8 0x0000.0000 Interrupt 32-35 Priority SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 64 Interrupt 156-159 Priority 0x4A0 PRI40 0x0000.0000 Interrupt 160-163 Priority 0x4A4 PRI41 0x0000.0000 Interrupt 164-167 Priority 0x4A8 PRI42 0x0000.0000 Interrupt 168-171 Priority Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 65 Configurable Fault Status 0xD2C HFAULTSTAT R/W1C 0x0000.0000 Hard Fault Status 0xD34 MMADDR Memory Management Fault Address 0xD38 FAULTADDR Bus Fault Address SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 66: Peripheral Registers

D2Ch HFAULTSTAT Hard Fault Status Section 3.3.1.22 D38h FAULTDDR Bus Fault Address Section 3.3.1.23 F00h SWTRIG Software Trigger Interrupt Section 3.3.1.24 Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 67: Actlr Register

IT folding, write buffer use for accesses to the default memory map, and interruption of multi-cycle instructions. By default, this register is set to provide optimum performance from the Cortex-M4 application processor in CC3200 and does not normally require modification. Figure 3-1. ACTLR Register... -

Page 68: Stctrl Register

0, the COUNT bit is set and an interrupt is generated if enabled by INTEN. The counter then loads the RELOAD value again and begins counting. Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 69: Streload Register

31-24 RESERVED 23-0 RELOAD Reload Value Value to load into the SysTick Current Value (STCURRENT) register when the counter reaches 0. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 70: Stcurrent Register

Writing to it with any value clears the register. Clearing this register also clears the COUNT bit of the STCTRL register. Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 71: En_0 To En_6 Register

0h (R) = On a read, indicates the interrupt is disabled. 1h (W) = On a write, enables the interrupt. 1h (R) = On a read, indicates the interrupt is enabled. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 72: Dis_0 To Dis_6 Register

0h (R) = On a read, indicates the interrupt is disabled. 1h (W) = On a write, no effect. 1h (R) = On a read, indicates the interrupt is enabled. Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 73: Pend_0 To Pend_6 Register

1h (W) = On a write, the corresponding interrupt is set to pending even if it is disabled. 1h (R) = On a read, indicates that the interrupt is pending. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 74: Unpend_0 To Unpend_6 Register

UNPEND6) register so that interrupt [n] is no longer pending. 1h (R) = On a read, indicates that the interrupt is pending. Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 75: Active_0 To Active_6 Register

Interrupt Active 0h = The corresponding interrupt is not active. 1h = The corresponding interrupt is active, or active and pending. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 76: Pri_0 To Pri_49 Register

Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 77: Cpuid Register

Constant Value Description 0xF Always reads as 0xF. 15-4 PARTNO C24h Part Number C24h = Cortex-M4 application processor in CC3200. Revision Number 1h = The pn value in the rnpn product revision identifier, for example, the 1 in r0p1. SWRU367D – June 2014 – Revised May 2018... -

Page 78: Intctrl Register

1h (W) = On a write, changes the SysTick exception state to pending. 1h (R) = On a read, indicates a SysTick exception is pending. Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 79 Interrupt Set Enable (ENn), Interrupt Clear Enable (DISn), Interrupt Set Pending (PENDn), Interrupt Clear Pending (UNPENDn), and Interrupt Priority (PRIn) registers. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 80: Vtable Register

Because there are 199 interrupts, the offset must be aligned on a 1024-byte boundary. RESERVED Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 81: Apint Register

0x05FA must be written to this field in order to change the bits in this register. On a read, 0xFA05 is returned. ENDIANESS Data Endianess The CC3200 implementation uses only little-endian mode so this is cleared to 0. 14-11 RESERVED... -

Page 82: Sysctrl Register

1h = When returning from Handler mode to Thread mode, enter sleep or deep sleep on return from an ISR. RESERVED Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 83: Cfgctrl Register

0h = Do not trap on unaligned halfword and word accesses. 1h = Trap on unaligned halfword and word accesses. An unaligned access generates a usage fault. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 84 0h = The processor can enter Thread mode only when no exception is active. 1h = The processor can enter Thread mode from any level under the control of an EXC_RETURN value. Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 85: Syspri1 Register

Configurable priority values are in the range 0-7, with lower values having higher priority. RESERVED SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 86: Syspri2 Register

SVCall Priority This field configures the priority level of SVCall. Configurable priority values are in the range 0-7, with lower values having higher priority. 28-0 RESERVED Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 87: Syspri3 Register

Debug Priority This field configures the priority level of Debug. Configurable priority values are in the range 0-7, with lower values having higher priority. RESERVED SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 88: Syshndctrl Register

0h = A bus fault exception is not pending. 1h = A bus fault exception is pending. Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 89 Caution above before setting this bit. 0h = Memory management fault is not active. 1h = Memory management fault is active. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 90: Faultstat Register

Usage Fault Status (UFAULTSTAT), bits 31:16 Bus Fault Status (BFAULTSTAT), bits 15:8 Memory Management Fault Status (MFAULTSTAT), bits 7:0 (Not applicable for CC3200) FAULTSTAT is byte accessible. FAULTSTAT or its subregisters can be accessed as follows: The... - Page 91 0h = No bus fault has occurred on unstacking for a return from exception. 1h = Unstacking for a return from exception has caused one or more bus faults. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 92 0h = No memory management fault has occurred on unstacking for a return from exception. 1h = Unstacking for a return from exception has caused one or more access violations. RESERVED Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

- Page 93 0h = An instruction access violation has not occurred. 1h = The processor attempted an instruction fetch from a location that does not permit execution. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 94: Hfaultstat Register

0h = No bus fault has occurred on a vector table read. 1h = A bus fault occurred on a vector table read. RESERVED Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 95: Faultddr Register

Fault Address When the FAULTADDRV bit of BFAULTSTAT is set, this field holds the address of the location that generated the bus fault. SWRU367D – June 2014 – Revised May 2018 Cortex-M4 Peripherals Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 96: Swtrig Register

Interrupt ID This field holds the interrupt ID of the required SGI. For example, a value of 0x3 generates an interrupt on IRQ3. Cortex-M4 Peripherals SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 97: Direct Memory Access (Dma)

SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) ........................... Topic Page ......................Overview ..................Functional Description ..................Register Description SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 98: Overview

Overview The CC3200 microcontroller includes a Direct Memory Access (DMA) controller, known as micro-DMA (μDMA). The μDMA controller provides a way to offload data transfer tasks from the Cortex-M4 processor, allowing for more efficient use of the processor and the available bus bandwidth. The μDMA controller can perform transfers between memory and peripherals. -

Page 99: Dma Channel Assignment

Peripherals are mapped at multiple places to address the application need where any combination of peripheral can be used in tandem. Figure 4-1. DMA Channel Assignment SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 100: Priority

Channel 1 – primary …. 0x1F0 Channel 31 – primary 0x200 Channel 0 – alternate 0x210 Channel 1 – alternate …. Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 101: Transfer Mode

Generally, auto mode is not used with a peripheral. When all the items have been transferred using auto mode, the μDMA controller sets the mode for that channel to stop. SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 102 Data flow can continue indefinitely this way, using the primary and alternate control structures to switch back and forth between buffers as the data flows to or from the peripheral. Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 103: Ping-Pong Mode

Functional Description www.ti.com Figure 4-2. Ping-Pong Mode SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 104 The primary control structure for the channel used for the operation is configured to copy from the task list to the alternate control structure. Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 105: Memory Scatter-Gather Mode

By using this method, the μDMA controller can transfer data to or from a peripheral from a set of arbitrary locations whenever the peripheral is ready to transfer data. SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 106: Peripheral Scatter-Gather Mode

Destination address increment Byte Source end pointer Peripheral FIFO register Destination end pointer End of data buffer in memory Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 107: Peripheral Interface

The ERRCLR bit is set if an error occurred. The error can be cleared by writing a 1 to the ERRCLR bit. SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 108: Register Description

0x038 DMA_PRIOSET 0x0000.0000 DMA Channel Priority 0x03C DMA_PRIOCLR DMA Channel Priority Clear 0x04C DMA_ERRCLR 0x0000.0000 DMA Bus Error Clear Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 109: Μdma Channel Control Structure

0x0, 0x10, 0x20 and so on. The alternate control structures are located at offsets 0x200, 0x210, 0x220, and so on. SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 110: Dma Registers

DMA Channel Source Address End Pointer Section 4.3.3.1 DMA_DSTENDP DMA Channel Destination Address End Pointer Section 4.3.3.2 DMA_CHCTL DMA Channel Control Word Section 4.3.3.3 Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 111: Dma_Srcendp Register

DMACHCTL register is 0x3), then this field points at the source location itself (such as a peripheral data register). SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 112: Dma_Dstendp Register

DMACHCTL register is 0x3), then this field points at the source location itself (such as a peripheral data register). Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 113: Dma_Chctl Register

3h = No increment Address remains set to the value of the Destination Address End Pointer (DMADSTENDP) for the channel 23-18 RESERVED SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 114 4h = Memory Scatter-Gather 5h = Alternate memory scatter gather 6h = Peripheral scatter gather 7h = Alternate peripheral scatter gather Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 115: Dma_(Offset_From_Dma_Base_Address) Registers

DMA Channel Map Select 2 Section 4.3.4.21 51Ch DMA_CHMAP3 DMA Channel Map Select 3 Section 4.3.4.22 FB0h DMA_PV DMA Peripheral Version Section 4.3.4.23 SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 116: Dma_Stat Register

9h = Done RESERVED MASTEN Master enable status. 0h = DMA controller is disabled 1h = DMA controller is enabled Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 117: Dma_Cfg Register

Type Reset Description 31-1 RESERVED MASTEN Controller Master enable 0h = Disables DMA controller 1h = Enables DMA controller SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 118: Dma_Ctlbase Register

This field contains the pointer to the base address of the channel control table. The base address must be 1024-byte aligned. RESERVED Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 119: Dma_Altbase Register

Reset Description 31-0 ADDR Alternate Channel Address. This field provides the base address of the alternate channel control structures SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 120: Dma_Waitstat Register

0h = The corresponding channel is not waiting on a request. 1h = The corresponding channel is waiting on a request. Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 121: Dma_Swreq Register

These bits are automatically cleared when the software request has been completed. 0h = No request generated 1h = Generate a software request for the corresponding channel. SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 122: Dma_Useburstset Register

0h = DMA channel [n] responds to single or burst requests. 1h = DMA channel [n] responds only to burst requests Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 123: Dma_Useburstclr Register

1h = Setting a bit clears the corresponding SET[n] bit in the DMAUSEBURSTSET register meaning that DMA channel [n] responds to single and burst requests SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 124: Dma_Reqmaskset Register

1h = The peripheral associated with channel [n] is not able to request DMA transfers. Channel [n] may be used for software- initiated transfers. Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 125: Dma_Reqmaskclr Register

1h = Setting a bit clears the corresponding SET[n] bit in the DMAREQMASKSET register meaning that the peripheral associated with channel [n] is enabled to request DMA transfers. SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 126: Dma_Enaset Register

DMAENACLR register or when the end of a DMA transfer occurs. 0h = DMA Channel [n] is disabled. 1h = DMA Channel [n] is enabled. Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 127: Dma_Enaclr Register

1h = Setting a bit clears the corresponding SET[n] bit in the DMAENASET register meaning that channel [n] is disabled for DMA transfers SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 128: Dma_Altset Register

0h = DMA channel [n] is using the primary control structure 1h = DMA channel [n] is using the alternate control structure Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 129: Dma_Altclr Register

1h = Setting a bit clears the corresponding SET[n] bit in the DMAALTSET register meaning that channel [n] is using the primary control structure SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 130: Dma_Prioset Register

0h = DMA channel [n] is using the default priority level 1h = DMA channel [n] is using the high priority level Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 131: Dma_Prioclr Register

1h = Setting a bit clears the corresponding SET[n] bit in the DMAPRIOSET register meaning that channel [n] is using the default priority level SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 132: Dma_Errclr Register

R/W1C DMA Bus Error Status 0h = No bus error is pending. 1h = A bus error is pending. Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 133: Dma_Chasgn Register

CHASGN_n Channel [n] Assignment Select 0h = Use the primary channel assignment. 1h = Use the secondary channel assignment. SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 134: Dma_Chmap0 Register

11-8 CH2SEL_n DMA channel 2 source select CH1SEL_n DMA channel 1 source select CH0SEL_n DMA channel 0 source select Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 135: Dma_Chmap1 Register

11-8 CH10SEL_n DMA channel 10 source select CH9SEL_n DMA channel 9 source select CH8SEL_n DMA channel 8 source select SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 136: Dma_Chmap2 Register

11-8 CH18SEL_n DMA channel 18 source select CH17SEL_n DMA channel 17 source select CH16SEL_n DMA channel 16 source select Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 137: Dma_Chmap3 Register

11-8 CH26SEL_n DMA channel 26 source select CH25SEL_n DMA channel 25 source select CH24SEL_n DMA channel 24 source select SWRU367D – June 2014 – Revised May 2018 Direct Memory Access (DMA) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 138: Dma_Pv Register

Table 4-32. DMA_PV Register Field Descriptions Field Type Reset Description 31-16 RESERVED 15-8 MAJVER Major Version MINVER Minor Version Direct Memory Access (DMA) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 139: General-Purpose Input/Outputs (Gpios)

General-Purpose Input/Outputs (GPIOs) ........................... Topic Page ......................Overview ..................Functional Description ....................Interrupt Control ................Initialization and Configuration ............... GPIO_REGISTER_MAP Registers SWRU367D – June 2014 – Revised May 2018 General-Purpose Input/Outputs (GPIOs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 140: Digital I/O Pads

Overview This chapter describes the general purpose input/output module and the I/O pad cells in the CC3200. The GPIO module is composed of 4 physical GPIO blocks, each corresponding to an individual GPIO port (Port 0, Port A1, Port A2, Port A3). The GPIO module supports up to 32 programmable input/output pins when GPIO function is selected in I/O pin muxing. -

Page 141: Gpiodata Write Example

GPIODATA bits 5, 4, and 0 with a single operation by using GPIODATA address alias 0x0C4 (offset address with regard to the base of the respective GPIO instance S0 to S4). Figure 5-3. GPIODATA Read Example SWRU367D – June 2014 – Revised May 2018 General-Purpose Input/Outputs (GPIOs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 142: Interrupt Control

Unmask the port by setting the IME field in the GPIOIM register. Table 5-1. GPIO Pad Configuration Examples GPIO Register Bit Value Configuration Digital Input (GPIO) General-Purpose Input/Outputs (GPIOs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 143: Gpio Interrupt Configuration Example

0=single edge GPIOIBE 1=both edges 0=Low level, or falling edge GPIOIEV 1=High level, or rising edge 0=masked GPIOIM 1=not masked SWRU367D – June 2014 – Revised May 2018 General-Purpose Input/Outputs (GPIOs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 144: Gpio_Register_Map Registers

GPIO Interrupt Clear Section 5.5.1.9 5.5.1 GPIO Register Description The remainder of this section lists and describes the GPIO registers. General-Purpose Input/Outputs (GPIOs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 145: Gpiodata Register

Writes to this register only affect bits that are not masked by ADDR[9:2] and are configured as outputs. SWRU367D – June 2014 – Revised May 2018 General-Purpose Input/Outputs (GPIOs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 146: Gpiodir Register

Description 31-8 RESERVED GPIO Data Direction 0h = Corresponding pin is an input. 1h = Corresponding pins is an output. General-Purpose Input/Outputs (GPIOs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 147: Gpiois Register

0h = The edge on the corresponding pin is detected (edge- sensitive). 1h = The level on the corresponding pin is detected (level-sensitive). SWRU367D – June 2014 – Revised May 2018 General-Purpose Input/Outputs (GPIOs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 148: Gpioibe Register

0h = Interrupt generation is controlled by the GPIO Interrupt Event (GPIOIEV) register. 1h = Both edges on the corresponding pin trigger an interrupt. General-Purpose Input/Outputs (GPIOs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 149: Gpioiev Register

0h = A falling edge or a Low level on the corresponding pin triggers an interrupt. 1h = A rising edge or a High level on the corresponding pin triggers an interrupt. SWRU367D – June 2014 – Revised May 2018 General-Purpose Input/Outputs (GPIOs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 150: Gpioim Register

0h = The interrupt from the corresponding pin is masked. 1h = The interrupt from the corresponding pin is sent to the interrupt controller. General-Purpose Input/Outputs (GPIOs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 151: Gpioris Register

0h = An interrupt condition has not occurred on the corresponding pin. 1h = An interrupt condition has occurred on the corresponding pin. SWRU367D – June 2014 – Revised May 2018 General-Purpose Input/Outputs (GPIOs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 152: Gpiomis Register

1h = An interrupt condition on the corresponding pin has triggered an interrupt to the interrupt controller. General-Purpose Input/Outputs (GPIOs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 153: Gpioicr Register

Description 31-8 RESERVED GPIO Interrupt Clear 0h = The corresponding interrupt is unaffected. 1h = The corresponding interrupt is cleared. SWRU367D – June 2014 – Revised May 2018 General-Purpose Input/Outputs (GPIOs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 154: Gpio_Trig_En Register Field Descriptions

GPIOA3 GPIO_25 GPIO_26 (Restricted Use; Antenna GPIOA3 Selection 1 Only) GPIO_27 (Restricted Use; Antenna GPIOA3 Selection 2 Only) GPIOA3 GPIO_28 General-Purpose Input/Outputs (GPIOs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 155 Table 5-14. GPIO Mapping (continued) GPIO Module Instance GPIO Bit GPIO # GPIOA3 GPIO_29 GPIOA3 GPIO_30 (PM/Dig Mux) GPIOA3 GPIO_31 (PM/Dig Mux) SWRU367D – June 2014 – Revised May 2018 General-Purpose Input/Outputs (GPIOs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 156: Universal Asynchronous Receivers/Transmitters (Uarts)

SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) ........................... Topic Page ......................Overview ..................Functional Description ..................Register Description Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 157: Overview

Overview www.ti.com Overview The CC3200 includes two Universal Asynchronous Receivers/Transmitters (UART) with the following features: • Programmable baud-rate generator allowing speeds up to 3 Mbps. • Separate 16×8 transmit (TX) and receive (RX) FIFOs to reduce CPU interrupt service loading •... -

Page 158: Uart Module Block Diagram

Figure 6-1. UART Module Block Diagram Functional Description Each CC3200 UART performs the functions of parallel-to-serial and serial-to-parallel conversions. The UART is configured for transmit and receive through the TXE and RXE bits of the UART Control (UARTCTL) register. Transmit and receive are both enabled out of reset. Before any control registers are programmed, the UART must be disabled by clearing the UARTEN bit in the UARTCTL register. -

Page 159: Uart Character Frame

Baud16 or fourth cycle of Baud8 depending on the setting of the HSE bit (bit 5) in UARTCTL. SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 160: Flow Control Mode

Out of reset, both FIFOs are disabled and act as 1-byte-deep holding registers. The FIFOs are enabled by setting the FEN bit in UARTLCRH. Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 161 TXRIS bit is set. It is cleared by performing a single write to the transmit FIFO, or by clearing the interrupt by writing a 1 to the TXIC bit. SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 162: Initialization And Configuration

1. Disable the UART by clearing the UARTEN bit in the UARTCTL register. 2. Write the integer portion of the BRD to the UARTIBRD register. Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 163: Register Description

0x040 UARTMIS 0x0000.0000 UART Masked Interrupt Status 0x044 UARTICR 0x0000.0000 UART Interrupt Clear 0x048 UARTDMACTL 0x0000.0000 UART DMA Control SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 164: Uart Registers

UARTMIS UART Masked Interrupt Status Section 6.3.1.11 UARTICR UART Interrupt Clear Section 6.3.1.12 UARTDMACTL UART DMA Control Section 6.3.1.13 Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 165: Uartdr Register

UART is written to this field. When read, this field contains the data that was received by the UART. SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 166: Uartrsr_Uartecr Register

FIFO. The next character is only enabled after the receive data input goes to a 1 (marking state) and the next valid start bit is received. Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 167 This bit is cleared to 0 by a write to UARTECR. In FIFO mode, this error is associated with the character at the top of the FIFO. SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 168: Uartfr Register

1h = If the FIFO is disabled (FEN is 0), the receive holding register is empty. If the FIFO is enabled (FEN is 1), the receive FIFO is empty. Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 169 1h = The U1CTS signal is asserted. This bit is implemented only on UART1 and is reserved for UART0 SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 170: Uartibrd Register Field Descriptions

UARTLCRH register. Table 6-7. UARTIBRD Register Field Descriptions Field Type Reset Description 31-16 RESERVED 15-0 DIVINT Integer Baud-Rate Divisor Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 171: Uartfbrd Register

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset Table 6-8. UARTFBRD Register Field Descriptions Field Type Reset Description 31-6 RESERVED DIVFRAC Fractional Baud-Rate Divisor SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 172: Uartlcrh Register

When in 7816 smartcard mode (the SMART bit is set in the UARTCTL register), the number of stop bits is forced to 2. Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 173 For the proper execution of the break command, software must set this bit for at least two frames (character periods). SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 174: Uartctl Register

U1RTS signal. If RTSEN is set, this bit is ignored on a write and should be ignored on read. Reserved Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 175 If the UART is disabled in the middle of transmission or reception, it completes the current character before stopping. SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 176: Uartifls Register

FIFO is completely empty and all data including stop bits have left the transmit serializer. In this case, the setting of TXIFLSEL is ignored. Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 177: Uartim Register

1h = An interrupt is sent to the interrupt controller when the BERIS bit in the UARTRIS register is set. SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 178 1h = An interrupt is sent to the interrupt controller when the CTSRIS bit in the UARTRIS register is set. RIIM Reserved Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 179: Uartris Register

1h = A break error has occurred. This bit is cleared by writing a 1 to the BEIC bit in the UARTICR register. SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 180 1h = Clear to Send used for software flow control. This bit is cleared by writing a 1 to the CTSIC bit in the UARTICR register. RIRIS Reserved Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 181: Uartmis Register

1h = An unmasked interrupt was signaled due to a break error. This bit is cleared by writing a 1 to the BEIC bit in the UARTICR register. SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 182 1h = An unmasked interrupt was signaled due to Clear to Send. This bit is cleared by writing a 1 to the CTSIC bit in the UARTICR register. RIMIS Reserved Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 183: Uarticr Register

Writing a 1 to this bit clears the RTRIS bit in the UARTRIS register and the RTMIS bit in the UARTMIS register. SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 184 Writing a 1 to this bit clears the CTSRIS bit in the UARTRIS register and the CTSMIS bit in the UARTMIS register. RIMIC Reserved Universal Asynchronous Receivers/Transmitters (UARTs) SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 185: Uartdmactl Register

Receive DMA Enable 0h = DMA for the receive FIFO is disabled. 1h = DMA for the receive FIFO is enabled. SWRU367D – June 2014 – Revised May 2018 Universal Asynchronous Receivers/Transmitters (UARTs) Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 186: Inter-Integrated Circuit (I2C) Interface

SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface ........................... Topic Page ......................Overview ..................Functional Description ....................Register Map Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 187: Overview

– Ability to execute single data transfers or burst data transfers using the RX and TX FIFOs in the SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 188: I2C Block Diagram

The CONFMODE bits in the GPIO_PAD_CONFIG register should be set to choose the I2C function. Set the I2CSDA and I2CSCL pins to open-drain using the IODEN bits of the GPIO_PAD_CONFIG register. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 189: I2C Bus Configuration

Pin R Functional Description The CC3200 has one instance of an I2C module comprised of both master and slave functions, identified by a unique address. A master-initiated communication generates the clock signal, SCL. For proper operation, the SDA and SCL pin must be configured as an open-drain signal. Both SDA and SCL signals must be connected to a positive supply voltage using a pullup resistor. -

Page 190: Start And Stop Conditions

The data on the SDA line must be stable during the high period of the clock, and the data line can only change when SCL is Low (see Figure 7-6). Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 191: Data Validity During Bit Transfer On The I2C Bus

4. The master does not generate a STOP condition, but instead writes another slave address to the I2CMSA register, then writes 0x3 to initiate the repeated START. SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 192 The OAR2SEL bit in the I2CSCSR register indicates if the ACKed address is the alternate address or not. When this bit is clear, it indicates either legacy operation or no address match. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 193: Supported Speed Modes

BURST transaction initiated. 7.2.2 Supported Speed Modes The I2C bus in the CC3200 can run in standard mode (100 kbps) or fast mode (400 kbps). The selected mode should match the speed of the other I2C devices on the bus. -

Page 194: Interrupts

The transmit FIFO can be assigned to the master, while the receive FIFO is assigned to the slave, and Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 195 TX FIFO fill level is less than the trigger set). If the I2CMBLEN register value is less than 4 and the TX FIFO is not full but more than trigger level, only dma_sreq asserts. Single requests are generated SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 196: Command Sequence Flow Charts

7.2.6.1 I2C Master Command Sequences The figures that follow show the command sequences available for the I2C master. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 197: Master Single Transmit

I2CMDR Read I2CMCS BUSBSY bit=0? Write ---0-111 to I2CMCS Read I2CMCS BUSY bit=0? Error Service ERROR bit=0? Idle SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 198: Master Single Receive

BUSBSY bit=0? Write ---00111 to I2CMCS Read I2CMCS BUSY bit=0? Error Service ERROR bit=0? Read data from I2CMDR Idle Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 199: Master Transmit Of Multiple Data Bytes

Index=n? to I2CMCS Error Service Write ---0-101 to I2CMCS Idle Read I2CMCS BUSY bit=0? Error Service ERROR bit=0? Idle SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 200: Master Receive Of Multiple Data Bytes

Error Service Write ---00101 to I2CMCS Idle Read I2CMCS BUSY bit=0? ERROR bit=0? Read data from Error Service I2CMDR Idle Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 201: Master Receive With Repeated Start After Master Transmit

Write ---01011 to I2CMCS Repeated START condition is generated with changing data Master operates in direction Master Receive mode Idle SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 202: Master Transmit With Repeated Start After Master Receive

Master Transmit mode Idle 7.2.6.2 I2C Slave Command Sequences Figure 7-13 presents the command sequence available for the I2C slave. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 203: Slave Command Sequence

0x0000.0007 (STOP, START, RUN). 9. Wait until the transmission completes by polling the BUSBSY bit of the I2CMCS register until the bit SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 204: Register Map

10. Check the ERROR bit in the I2CMCS register to confirm the transmit was acknowledged. Register Map Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 205: I2C Registers

I2C FIFO Status Section 7.3.1.25 FC0h I2CPP I2C Peripheral Properties Section 7.3.1.26 FC4h I2CPC I2C Peripheral Configuration Section 7.3.1.27 SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 206: I2Cmsa Register

1h = Receive The R/S bit specifies if the next master operation is a Receive (High) or Transmit (Low). Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 207: I2Cmcs Register

0h (R) = The I2C controller is not idle. 1h (W) = The bus transaction is a quick command. 1h (R) = The I2C controller is idle. SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 208 1h (W) = The master is able to transmit or receive data. Note that this bit cannot be set in Burst mode. 1h (R) = The controller is busy. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 209: I2Cmdr Register

Table 7-6. I2CMDR Register Field Descriptions Field Type Reset Description 31-8 RESERVED DATA This byte contains the data transferred during a transaction. SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 210: I2Cmtpr Register

SCL_LP is the SCL Low period (fixed at 6). SCL_HP is the SCL High period (fixed at 4). CLK_PRD is the system clock period in ns. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 211: I2Cmimr Register

1h = The TX FIFO Request interrupt is sent to the interrupt controller when the TXRIS bit in the I2CMRIS register is set. SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 212 1h = The master interrupt is sent to the interrupt controller when the RIS bit in the I2CMRIS register is set. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 213: I2Cmris Register

This bit is cleared by writing a 1 to the ARBLOSTIC bit in the I2CMICR register. 0h = No interrupt 1h = The Arbitration Lost interrupt is pending. SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 214 Value Description This bit is cleared by writing a 1 to the IC bit in the I2CMICR register. 0h = No interrupt. 1h = A master interrupt is pending. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 215: I2Cmmis Register

This bit is cleared by writing a 1 to the ARBLOSTIC bit in the I2CMICR register. 0h = No interrupt. 1h = An unmasked Arbitration Lost interrupt was signaled and is pending. SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 216 This bit is cleared by writing a 1 to the CLKIC bit in the I2CMICR register. 0h = No interrupt. 1h = An unmasked clock timeout interrupt was signaled and is pending. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 217: I2Cmicr Register

Writing a 1 to this bit clears the STARTRIS bit in the I2CMRIS register and the STARTMIS bit in the I2CMMIS register. A read of this register returns no meaningful data. SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 218 Writing a 1 to this bit clears the RIS bit in the I2CMRIS register and the MIS bit in the I2CMMIS register. A read of this register returns no meaningful data. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 219: I2Cmcr Register

1h = Master mode is enabled. RESERVED LPBK I2C Loopback 0h = Normal operation. 1h = The controller in a test mode loopback configuration. SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 220: I2Cmclkocnt Register

This field contains the upper 8 bits of a 12-bit counter for the clock low timeout count. Note: The value of CNTL must be greater than 0x1. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 221: I2Cmbmon Register

1h = The I2CSDA signal is high. I2C SCL Status 0h = The I2CSCL signal is low. 1h = The I2CSCL signal is high. SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 222: I2Cmblen Register

Transaction. If BURST is enabled this register must be set to a non-zero value otherwise an error will occur. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 223: I2Cmbcnt Register

Description 31-8 RESERVED CNTL I2C Master Burst Count This field contains the current count-down value of the BURST transaction. SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 224: I2Csoar Register

Reset Description 31-7 RESERVED I2C Slave Own Address This field specifies bits A6 through A0 of the slave address. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 225: I2Cscsr Register

1h (W) = Enables RX FIFO 1h (R) = The first byte following the slave s own address has been received. SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... - Page 226 I2C master and is using clock stretching to delay the master until the data has been read from the I2CSDR register. Inter-Integrated Circuit (I2C) Interface SWRU367D – June 2014 – Revised May 2018 Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated...

-

Page 227: I2Csdr Register

RESERVED DATA Data for Transfer This field contains the data for transfer during a slave receive or transmit operation. SWRU367D – June 2014 – Revised May 2018 Inter-Integrated Circuit (I2C) Interface Submit Documentation Feedback Copyright © 2014–2018, Texas Instruments Incorporated... -

Page 228: I2Csimr Register