NXP Semiconductors i.MX 8M Plus User Manual

Hide thumbs

Also See for i.MX 8M Plus:

- User manual (21 pages) ,

- Instruction manual (66 pages) ,

- Quick start manual (85 pages)

Summary of Contents for NXP Semiconductors i.MX 8M Plus

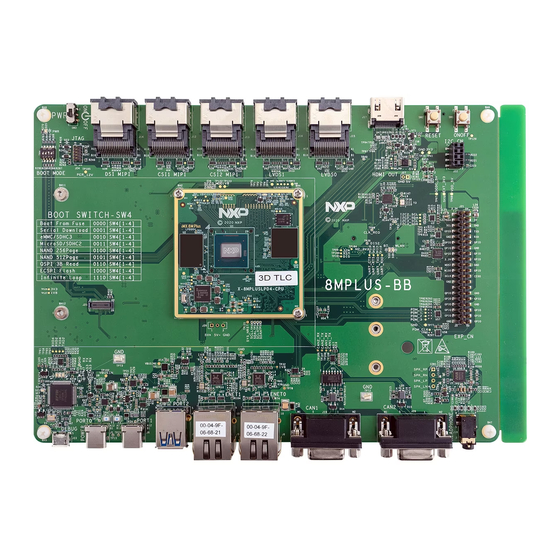

- Page 1 NXP Semiconductors Document identifier: IMX8MPHDG User's Guide Rev. 0, 03/2021 i.MX 8M Plus Hardware Developer’s Guide...

-

Page 2: Chapter 1 Overview

This document supports the i.MX 8M Plus (15 x 15 mm package). 1.2 Essential references This guide is supplementary to the i.MX 8M Plus series chip reference manuals and data sheets. For reflow profile and thermal limits during soldering, see General Soldering Temperature Process Guidelines (document AN3300). These documents are available on www.nxp.com/i.MX8MPLUS. -

Page 3: Related Documentation

In this document, notation for all logical, bit-wise, arithmetic, comparison, and assignment operations follow C Language conventions. 1.6 Acronyms and abbreviations Table 2 defines the acronyms and abbreviations used in this document. i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide 3 / 50... - Page 4 Input output Buffer Information Specification IOMUX i.MX 8M Plus chip-level I/O multiplexing JTAG Joint Test Action Group Keypad Port Peripheral Table continues on the next page... i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide 4 / 50...

- Page 5 Power Management Integrated Circuit Power-On Reset Plated Through Hole PCB (that is, no microvias) RGMII Reduced Gigabit Media Independent Interface (Ethernet) RMII Reduced Media Independent Interface (Ethernet) Read-Only Memory i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide 5 / 50...

-

Page 6: Chapter 2 I.mx 8M Plus Design Checklist

8M Plus design checklist This document provides a design checklist for the i.MX 8M Plus (15 x 15 mm package) processor. The design checklist tables recommend optimal design and provide explanations to help users understand better. All supplemental tables referenced by the checklist appear in sections following the design checklist tables. - Page 7 DDR4 system will be higher compared with cannot run in low frequency, such as 100 MTS. LPDDR4 system. NOTE Refer to i.MX 8M Plus data sheet for supported DDR chip selects and bus width configurations. Table 5. I C recommendations Check box...

- Page 8 POR_B pin of the CPU. When POR_B is voltage. This functionality is controlled by the PMIC asserted (low) on the i.MX 8M Plus, the output (PCA9450CHN) on EVK. PMIC_ON_REQ remains asserted (high).

- Page 9 Dummy read strobe generated by device does not provide DQS. FlexSPI controller and looped back Table continues on the next page... i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide 9 / 50...

- Page 10 µW. Follow the manufacturer’s recommendation external 32.768 KHz clock can be fed into RTC_XTALI for loading capacitance. Use short traces between to provide the RTC clock for the i.MX 8M Plus. See the crystal and the processor, with a ground item #3.

- Page 11 VDD_PCI_0P8, VDD_USB_0P8 NVCC_DRAM — — — VDD_ARM — — — VDD_SNVS_0P8_CAP — — — — NVCC_SNVS_1P8 — — — — Table continues on the next page... i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide 11 / 50...

- Page 12 NXP Semiconductors i.MX 8M Plus design checklist Table 13. Decoupling capacitors recommendations (i.MX 8M Plus) (continued) Checkbox Supply 0.22 µF 1 µF 4.7 µF 10 µF Notes VDD_24M_XTAL_1P8, These 14 power rails are combined on EVK VDD_EARC_1P8, VDD_ANA1_1P8, VDD_ANA2_1P8, VDD_ARM_PLL_1P8,...

- Page 13 NXP Semiconductors i.MX 8M Plus design checklist Table 13. Decoupling capacitors recommendations (i.MX 8M Plus) (continued) Checkbox Supply 0.22 µF 1 µF 4.7 µF 10 µF Notes • 10 μF --- CL05A106MQ5NUNC Table 14. PCB design recommendations Check box Recommendations...

-

Page 14: General Recommendations

2.4 General recommendations More than one software operating environment can run on the i.MX 8M Plus platforms concurrently. Peripherals on these SoCs are accessible to all software operating environments. Conflict occurs when more than one software operating environment reads or writes the state of the same peripheral. - Page 15 In this case, customer needs to implement customized software solutions like: RPMSG Client/server-style cooperative device drivers or Peripheral Exclusive Access using a Mutex solution implemented using SEMA42. Implementation on the i.MX 8M Plus is up to the customer’s Software Architecture.

-

Page 16: Chapter 3 I.mx 8M Plus Layout/Routing Recommendations

3.3.1 Stack-up recommendation (i.MX 8M Plus) Due to the number of balls on the i.MX 8M Plus processor in the 15 mm x 15 mm package, a minimum 6-layer PCB stack-up is recommended. For the 6 layers on the PCB, at least 1 layer need to be dedicated to power on routing to meet the IR drop target of 2% for the i.MX 8M Plus CPU power rails. - Page 17 • PCB material: the material used on EVK is TU768. 3.3.2 Manufacturing recommendation (i.MX 8M Plus) Since the i.MX 8M Plus processor uses 0.5mm-pitch BGA package, the PCB technology must meet below requirement to fully fanout all the signals of the processor using PTH(plated through holes).

- Page 18 3.94 mil Signal 7628 RC47% Dielectric 12.88 mil 2116 RC58% 3.91 Power Dielectric Core 0.3MM 1/1 4.47 11.81 mil Power Table continues on the next page... i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide 18 / 50...

- Page 19 3.4 DDR design recommendations 3.4.1 DDR connection information The i.MX 8M Plus processor can be used with LPDDR4 or DDR4 memory. Since these memory types have different I/O signals, there are 38 generically-named functional balls, depending on the type of memory used. See...

- Page 20 DRAM_AC29 CA1_B DRAM_AC30 CA2_B A10 / AP DRAM_AC31 CA3_B DRAM_AC32 CA4_B DRAM_AC33 CA5_B CAS_n / A15 DRAM_AC34 WE_n / A14 Table continues on the next page... i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide 20 / 50...

- Page 21 CS1_n 3.4.2 LPDDR4-4000 design recommendations The following list provides some generic guidelines that should be adhered to when implementing an i.MX 8M Plus design using LPDDR4. 1. It is expected that the layout engineer and design team already has experience and training with DDR designs at speeds of 2 GHz / 4000 MT/s.

- Page 22 8. Byte swapping within each 16-bit channel is OK. Bit swapping within each slice/byte lane is OK. 9. Bit swapping of Command/Address (CA[5:0]) pins is NOT allowed. 10. i.MX 8M Plus does not drive ODT_CA signals. The ODT_CA balls on the LPDDR4 devices should be connected directly or through a resistor to the VDD2 supply.

- Page 23 145.1 Total Net Delay 105.3 39.8 Vias are L1-> L3->L1 DRAM_CKE0_A 145.1 Total Net Delay 102.8 43.1 Vias are L1-> L3->L1 DRAM_CKE1_A 145.9 Total Net Delay i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide 23 / 50...

- Page 24 Figure 5 show the placement and routing of the LPDDR4 signals on the i.MX 8M Plus EVK board. The CLK and DQS signals are routed on bottom layer to save routing space on top layer and layer 3. Chanel A data byte lane 1 and channel B data byte lane 0 signals are routed on top layer, and Chanel A data byte lane 0, channel B data byte lane 1 and CA/CTL signals are routed on layer 3.

- Page 25 NXP Semiconductors i.MX 8M Plus layout/routing recommendations Figure 3. i.MX 8M Plus EVK board LPDDR4 routing (Top Layer) Figure 4. i.MX 8M Plus EVK board LPDDR4 routing (Layer 3) i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide...

- Page 26 The simulation architecture includes the DDR controller (that is, the i.MX 8M Plus processor), the PCB and the DRAM device. The IBIS model for the i.MX 8M Plus processor is available from NXP. The DRAM device IBIS model must be obtained from the memory vendor.

- Page 27 Figure 6. Example of simulated eye width 3.4.4 i.MX 8M Plus DDR package delay When performing the required delay matching for LPDDR4/DDR4 routing, the substrate routing within the i.MX 8M Plus package need to be accounted for and included in the match calculation.

- Page 28 NXP Semiconductors i.MX 8M Plus layout/routing recommendations Table 23. i.MX 8M Plus DDR package trace delays (continued) Ball Name Delay (ps) Ball name Delay (ps) DRAM_AC09 33.5 DRAM_DQS3_P 48.2 DRAM_AC10 61.7 DRAM_DQ00 50.1 DRAM_AC11 71.6 DRAM_DQ01 56.5 DRAM_AC12 28.3 DRAM_DQ02 60.9...

- Page 29 53.8 3.4.5 JEDEC specification compliance The i.MX 8M Plus processors are designed and tested to work with the JEDEC JESD209-4A–compliant LPDDR4 and JEDEC JESD79-3F-compliant DDR3L memories. Timing diagrams and tolerances required to work with these memories are specified in the respective documents and are not reprinted here.

- Page 30 50 pF load board to the signal, and the capacitance load driving capability of the i.MX 8M Plus MIPI-DSI LP driver is 70 pF, also considering the i.MX 8M Plus chip itself can have up to 10 pF capacitance, so the final allowed maximum capacitance of the PCB trace will be 10 pF.

- Page 31 ONE PMIC part for all kinds of DDR memories. Figure 7 shows a block diagram of the power tree of the NXP i.MX 8M Plus EVK board. It uses a single PCA9450CHN PMIC to power ON rails of the processor.

- Page 32 NXP Semiconductors i.MX 8M Plus layout/routing recommendations Figure 7. i.MX 8M Plus development platform power distribution block diagram i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide 32 / 50...

-

Page 33: Usb Connectivity

3.8 PCIE connectivity The i.MX 8M Plus has one PCIE interface. There is a pair of pins with the name of PCIE _CLK_P/N. These pins are bi-directional which can either be used to feed 100 MHz reference clock to the PHY from external clock source, or to output an internal generated 100 MHz reference clock to PCIE connector or PCIE device. -

Page 34: Hdmi Connectivity

3.10 Unused input/output terminations 3.10.1 i.MX 8M Plus unused input/output guidance For the i.MX 8M Plus, the I/Os and power rails of an unused function can be terminated to reduce overall board power. Table 28 lists connectivity examples for unused functions except MIPI and USB. The use case for MIPI and USB is a little more complex... - Page 35 NXP Semiconductors i.MX 8M Plus layout/routing recommendations Table 29. i.MX 8M Plus MIPI strapping recommendations (continued) Use case Ball name Recommendation MIPI_DSI_CLK_P/N, MIPI_DSI_Dx_P/N VDD_MIPI_1P8, VDD_MIPI_0P8, Supply MIPI_VREG1_CAP Floating VDD_MIPI_1P2_CAP Connect to outside cap Only MIPI-CSI1 & MIPI_TEST_DNU Floating MPI-CSI2 used...

- Page 36 NXP Semiconductors i.MX 8M Plus layout/routing recommendations Table 29. i.MX 8M Plus MIPI strapping recommendations (continued) Use case Ball name Recommendation VDD_MIPI_1P8, VDD_MIPI_0P8 Floating VDD_MIPI_1P2_CAP/ MIPI_VREG1_CAP Floating MIPI_TEST_DNU Floating All MIPI-CSI1/2 and DSI not used MIPI_CSI1_CLK_P/N, MIPI_CSI1_Dx_P/N Floating MIPI_CSI2_CLK_P/N, MIPI_CSI2_Dx_P/N...

-

Page 37: Chapter 4 Avoiding Board Bring-Up Problems

• Make two measurements: the first after initial board power-up and the second while running a heavy use-case that stresses the i.MX 8M Plus processor. Ensure that the i.MX 8M Plus power supply meets the DC electrical specifications as listed in the chip-specific data sheet. See Table 31 for a sample voltage report table. - Page 38 Although not required, the use of low jitter external oscillators to feed CLKIN_1/2 can be an advantage if low jitter or special frequency clock sources are required by modules driven by CLKIN_1/2. See the CCM chapter in the i.MX 8M Plus chip reference manual for details.

- Page 39 • During initial power-on while asserting the POR_B reset signal, ensure that 24 MHz and 32.768 kHz clock is active before releasing POR_B. • Follow the recommended power-up sequence specified in the i.MX 8M Plus data sheet. • Ensure the POR_B signal remains asserted (low) until all voltage rails associated with bootup are ON.

- Page 40 Checklist item Details Owner &Status Verify basic operation of the i.MX 8M Plus in system. The on-chip internal RAM starts at address 0x0090 0000 and is Access internal RAM 128 Kbytes in density. Perform a basic test by performing a write-read-verify operation to the internal RAM.

-

Page 41: Chapter 5 Using Bsdl For Board-Level Testing

• On-chip Fuse bits. The JTAG_MOD pin state controls the selection of the JTAG to the core logic or boundary scan operation. See the following references for further information: i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide 41 / 50... - Page 42 Table 34 shows pin functionality of DDR4 DRAM device in connectivity test mode. i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide 42 / 50...

- Page 43 To make the DRAM device enter connectivity test mode, TEN pin should be pulled HIGH, and RESET_n pin should also be held HIGH. However, in i.MX 8M Plus A0 silicon, the output of DRAM_RESET_N pin will be fixed LOW in boundary scan mode and cannot be controlled by the boundary scan logic.

-

Page 44: Chapter 6 Thermal Considerations

Thermal considerations 6.1 Introduction This chapter introduces basic thermal considerations that need to be considered, when designing an i.MX 8M Plus processor- based system. PCBs should be designed with the thermal requirements factored in early as only remedial actions are possible after. -

Page 45: Thermal Resistance

6.7 Component placement The i.MX 8M Plus processor should always be placed away from edges in the center of the PCB so that heat can effectively spread in all directions. Placing the device on the edge or even on the corner of the PCB significantly reduces heat transfer from the device and dissipation capabilities of the to the PCB, as the heat cannot efficiently spread in the directions where the edges are present. - Page 46 If a narrow gap at the bottom side cannot be avoided (quite common for System on Modules - SOMs), it should be considered to fill the gap under the i.MX 8M Plus processor by thermally conductive gap filler. To further improve heat transfer, exposed copper pads should be added to the base board at the mounting spot of the filler.

- Page 47 • All unused module clocks should be turned off (Dynamically handled by NXP Linux BSP) • Customers are encouraged to use the latest Linux BSP GA release available on nxp.com, that leverages the i.MX 8M Plus processor power management features and incorporates various Linux software power management techniques For more details on the power consumption, refer to AN13054.

- Page 48 Item Activity Check Determine the Tj for the i.MX 8M Plus device to use (Industrial, consumer etc.) Factor in board design considerations early (PCB layers, metallization, layout, component placement) Run thermal simulations to determine the best thermal management approach using form factor...

-

Page 49: Chapter 7 Revision History

NXP Semiconductors Chapter 7 Revision history Table 35. Revision history Revision number Date Substantive changes 03/2021 Initial release i.MX 8M Plus Hardware Developer’s Guide, Rev. 0, 03/2021 User's Guide 49 / 50... - Page 50 Right to make changes - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Need help?

Do you have a question about the i.MX 8M Plus and is the answer not in the manual?

Questions and answers