Silicon Laboratories EFM32 Application Note

Hide thumbs

Also See for EFM32:

- Application note (27 pages) ,

- Hardware design manuallines (21 pages) ,

- Quick start manual (16 pages)

Table of Contents

Advertisement

Quick Links

EFM32 Interrupt Handling

AN0039 - Application Note

Introduction

This application note is an introduction to interrupts and wake-up handling in the

EFM32. It includes ways to optimize for low latency wake-up, interrupt prioritization

and energy saving operation.

This application note includes:

• This PDF document

• Source files (zip)

• Example C code

• Multiple IDE projects

...the world's most energy friendly microcontrollers

Advertisement

Table of Contents

Summary of Contents for Silicon Laboratories EFM32

- Page 1 AN0039 - Application Note Introduction This application note is an introduction to interrupts and wake-up handling in the EFM32. It includes ways to optimize for low latency wake-up, interrupt prioritization and energy saving operation. This application note includes: • This PDF document •...

-

Page 2: Interrupt Theory

ISR and SW needed to determine which source triggered the IRQ. In modern architectures like the ARM Cortex-M in the EFM32, each IRQ has its own ISR. The starting address for each ISR is stored in an interrupt vector table. - Page 3 ...the world's most energy friendly microcontrollers Figure 1.2. Nested Interrupts Interrupt 2 with higher priority than interrupt 1 Interrupt 1 ISR 1 Main thread ISR 2 www.silabs.com 2013-09-16 - an0039_Rev1.04...

-

Page 4: Interrupts In The Efm32

IRQ lines and switches the CPU execution to the triggered IRQs address in the vector table. Figure 2.1 (p. 4) shows an overview of how interrupts are handled in the EFM32. Most of the peripherals in the EFM32 can generate interrupts and control one or more interrupt lines (IRQ) each. - Page 5 (System Control Space). More information on the NVIC can be found in the EFM32 Cortex-M3 Reference Manual. As shown in Figure 2.1 (p. 4) , each IRQ will set a Pending bit when asserted. This pending bit will generate an interrupt request to the CPU if the corresponding enable bit (SETENA[n] in Figure 2.1 (p.

- Page 6 VCMP 2.2.1 Interrupt Priority Each IRQ in the EFM32 has 3 bits in the Priority Level Registers (IPRn) controlling interrupt priority. A low value means a high priority. These bits are used to configure two types of priority: • Preempt priority www.silabs.com...

-

Page 7: Sleep Operation

If there is no other work for the CPU to do while waiting for an interrupt to trigger, energy can be saved by putting the CPU to sleep until the interrupt triggered. In the EFM32 there are two ways of going to www.silabs.com... - Page 8 The Wait For Event instruction (__WFE();), causes immediate entry to EM1/2/3. The CPU will wake up once it receives an event. In the EFM32 an event can be generated by a pending interrupt if the Send Event on Pending Interrupt bit (SEVONPEND)in the System Control Register is set. Note that if the interrupt is also enabled, the pending interrupt will also cause the ISR to be executed after waking up.

- Page 9 ...the world's most energy friendly microcontrollers Note that when using other interrupts at the same time as using WFE, the event status bit must be cleared every time an interrupt executes. 2.3.3 Continuous Sleep With SLEEPONEXIT Normally when the ISR is done, CPU execution returns to where it left off. However, if the SLEEPONEXIT bit in the System Control Register (SCR) is set to 1 the device enters sleep (depth set by DEEPSLEEP bit) directly when finishing the ISR without returning to main.

-

Page 10: Cmsis

(TIMER_IntEnable-function below) are all handled by the emlib functions (functions for TIMER0 are found in efm32_timer.h). Please note that the emlib and CMSIS functions themselves are shared between all EFM32 devices and individual differences between the sub-series are handled internally in the functions. -

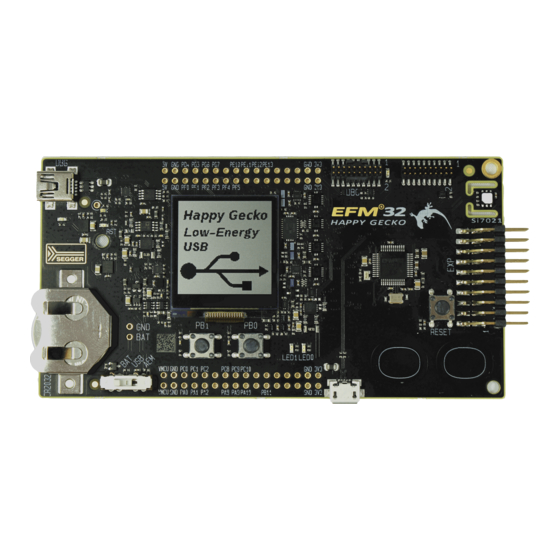

Page 11: Software Examples

...the world's most energy friendly microcontrollers 4 Software examples The included examples are written for the Tiny and Giant Gecko starter kits and their onboard devices EFM32TG840F32 and EFM32GG990F1024, respectively. Source files and projects for several IDEs are also included with this application note. 4.1 WFI In the wait_for_interrupt example project, TIMER0 is set to Up/Down mode and is configured to trigger interrupts when an overflow or underflow occurs. -

Page 12: Sleep-On-Exit

...the world's most energy friendly microcontrollers 4.3 Sleep-on-Exit The sleep_on_exit example project sets up TIMER0 in Up/Count mode to give overflow interrupts every second. The SLEEPONEXIT bit is set and the device is put in EM1. Execution will then not return to main until SLEEPONEXIT is cleared. -

Page 13: Further Reading

...the world's most energy friendly microcontrollers 5 Further Reading Details on the interrupt capabilities of each peripheral in the EFM32 devices can be found in the reference manual for the device. Cortex-internal parts, such as the NVIC, is documented in the EFM32 Cortex-M3 Reference Manual. -

Page 14: Revision History

...the world's most energy friendly microcontrollers 6 Revision History 6.1 Revision 1.04 2013-09-03 New cover layout 6.2 Revision 1.03 2013-05-08 Added software projects for ARM-GCC and Atollic TrueStudio. Specified how to clear event status bit in PDF document and in wait_for_event examples. 6.3 Revision 1.02 2012-11-12 Adapted software projects to new kit-driver and bsp structure. -

Page 15: Disclaimer And Trademarks

A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. -

Page 16: Contact Information

...the world's most energy friendly microcontrollers B Contact Information Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 Please visit the Silicon Labs Technical Support web page: http://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request. www.silabs.com 2013-09-16 - an0039_Rev1.04... -

Page 17: Table Of Contents

...the world's most energy friendly microcontrollers Table of Contents 1. Interrupt Theory ............................2 2. Interrupts in the EFM32 ..........................4 2.1. Peripheral IRQ Generation ....................... 4 2.2. The Nested Vector Interrupt Controller (NVIC) ..................4 2.3. Sleep Operation ..........................7 3. - Page 18 ...the world's most energy friendly microcontrollers List of Figures 1.1. Basic Interrupt Operation ......................... 2 1.2. Nested Interrupts ............................ 3 2.1. Interrupt overview ........................... 4 2.2. Definition of Priority Fields in Priority Level Register ..................7 2.3. Latency when entering interrupt handlers ....................7 4.1.

- Page 19 ...the world's most energy friendly microcontrollers List of Tables 2.1. EFM32 Interrupts ............................ 6 2.2. Entering Energy Modes with WFI/WFE ....................... 8 www.silabs.com 2013-09-16 - an0039_Rev1.04...

- Page 20 ...the world's most energy friendly microcontrollers List of Examples 2.1. TIMER0 interrupt flags/conditions ....................... 4 2.2. Clearing event status bit: ......................... 8 3.1. A TIMER0 ISR: ............................ 10 3.2. Enabling TIMER0 Overflow Interrupt: ......................10 www.silabs.com 2013-09-16 - an0039_Rev1.04...

Need help?

Do you have a question about the EFM32 and is the answer not in the manual?

Questions and answers