Altera Nios II Hardware Development Manual

Hide thumbs

Also See for Nios II:

- User manual (288 pages) ,

- Reference manual (56 pages) ,

- Quick start manual (3 pages)

Summary of Contents for Altera Nios II

- Page 1 Nios II Hardware Development Tutorial Nios II Hardware Development Tutorial 101 Innovation Drive San Jose, CA 95134 www.altera.com TU-N2HWDV-4.0 Subscribe...

- Page 2 © 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at www.altera.com/common/legal.html.

-

Page 3: Table Of Contents

Create a New Nios II Application and BSP from Template ......1–32... - Page 4 Contents Nios II Hardware Development Tutorial May 2011 Altera Corporation...

-

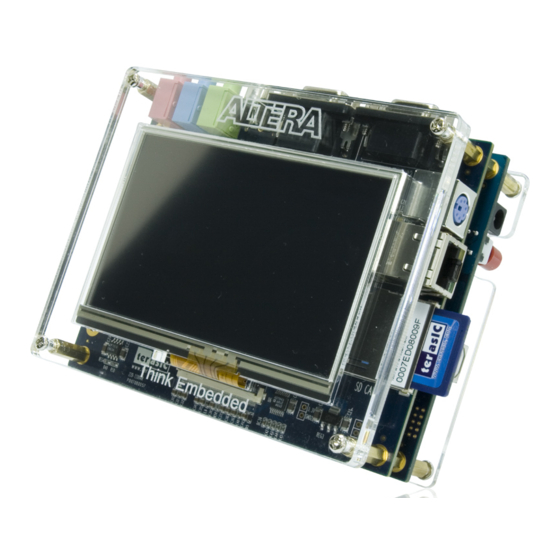

Page 5: Chapter 1. Nios Ii Hardware Development

Nios II system and interfaces with components on Altera development boards. The tutorial is a good starting point if you are new to the Nios II processor or the general concept of building embedded systems in FPGAs. -

Page 6: Software And Hardware Requirements

1–1, other logic can exist within the FPGA alongside the Nios II system. In fact, most FPGA designs with a Nios II system also include other logic. A Nios II system can interact with other on-chip logic, depending on the needs of the overall system. -

Page 7: Opencore Plus Evaluation

■ Program a device and verify your design in hardware You need to purchase a license for the Nios II processor only when you are completely satisfied with its functionality and performance, and want to use your design in production. -

Page 8: Nios Ii System Development Flow

Chapter 1: Nios II Hardware Development Nios II System Development Flow Nios II System Development Flow This section discusses the complete design flow for creating a Nios II system and prototyping it on a target board. Figure 1–2 shows the Nios II system development flow. -

Page 9: Analyzing System Requirements

You can select from a list of standard processor cores and components provided with the Nios II EDS. You can also add your own custom hardware to accelerate system performance. You can add custom instruction logic to the Nios II core which accelerates CPU performance, or you can add a custom component which offloads tasks from the CPU. -

Page 10: Integrating The Qsys System Into The Quartus Ii Project

Nios II SBT for Eclipse projects. To create a new Nios II C/C++ application project, the Nios II SBT for Eclipse uses information from the .sopcinfo file. You also need the .sof file to configure the FPGA before running and debugging the application project on target hardware. -

Page 11: Running And Debugging Software On The Target Board

Iteratively Creating a Nios II System A common technique for building a complex Nios II system is to start with a simpler Qsys system, and iteratively add to it. At each iteration, you can verify that the system performs as expected. You might choose to verify the fundamental components of a system, such as the processor, memory, and communication channels, before adding more complex components. -

Page 12: Verifying The System With Hardware Simulation Tools

1–35. Install the Design Files Before you proceed, you must install the Quartus II software and the Nios II EDS. You must also download tutorial design files from the Altera web site. The design files provide a ready-made Quartus II project to use as a starting point. -

Page 13: Analyze System Requirements

Nios II systems. ■ Build a Nios II system that works on any board with an Altera FPGA. The entire system must use only on-chip resources, and not rely on the target board. The design should conserve on-chip logic and memory resources so it can fit in a ■... -

Page 14: Create A New Qsys System

Create a New Qsys System You use Qsys to generate the Nios II processor system, adding the desired components, and configuring how they connect together. To create a new Qsys system, click Qsys on the Tools menu in the Quartus II software. Qsys starts and displays the System Contents tab. -

Page 15: Define The System In Qsys

You use Qsys to define the hardware characteristics of the Nios II system, such as which Nios II core to use, and what components to include in the system. Qsys does not define software behavior, such as where in memory to store instructions or where to send the stderr character stream. -

Page 16: Add The On-Chip Memory

Chapter 1: Nios II Hardware Development Creating the Design Example Perform the following steps: 1. On the Project Settings tab, select the Device Family that matches the Altera FPGA you are targeting. If a warning appears stating the selected device family does not match the Quartus project settings, ignore the warning. - Page 17 Chapter 1: Nios II Hardware Development 1–13 Creating the Design Example Figure 1–5 shows the On-Chip Memory (RAM or ROM) parameter editor. Figure 1–5. On-Chip Memory Parameter Editor 5. Click Finish. You return to Qsys. 6. Click the System Contents tab. An instance of the on-chip memory appears in the system contents table.

-

Page 18: Add The Nios Ii Processor Core

Nios II programs easier to read and understand. Add the Nios II Processor Core In this section you add the Nios II/s core and configure it to use 2 KB of on-chip instruction cache memory. For educational purposes, the tutorial design example uses the Nios II/s (standard) core, which provides a balanced trade-off between performance and resource utilization. - Page 19 1–15 Creating the Design Example Figure 1–6 shows the Core Nios II tab of the Nios II Processor parameter editor. Figure 1–6. Nios II Parameter Editor – Core Nios II Tab 15. Click the Caches and Memory Interfaces tab. Figure 1–7 shows the GUI.

- Page 20 Instantiating the Nios II Processor in Qsys chapter of the Nios II Processor Reference Handbook. For more information about connecting memory to Nios II systems, refer to the System Design with Qsys section of Volume 1: Design and Synthesis of the Quartus II Handbook.

-

Page 21: Add The Jtag Uart

Add the JTAG UART The JTAG UART provides a convenient way to communicate character data with the Nios II processor through the USB-Blaster download cable. Perform the following steps to add the JTAG UART: 1. On the Component Library tab, expand Interface Protocols, expand Serial, and then click JTAG UART. -

Page 22: Add The Interval Timer

8. Connect the data_master port of the Nios II processor to the avalan_jtag_slave port of the JTAG UART. The instruction_master port of the Nios II processor does not connect to the JTAG UART because the JTAG UART is not a memory device and cannot send instructions to the Nios II processor. -

Page 23: Add The System Id Peripheral

8. Connect the clk_reset port of the clk_0 clock source to the reset port of the interval timer. 9. Connect the data_master port of the Nios II processor to the s1 port of the interval timer. For more information about the timer, refer to the Timer Core chapter in the... -

Page 24: Add The Pio

7. Connect the clk_reset port of the clk_0 clock source to the reset port of the system ID peripheral. 8. Connect the data_master port of the Nios II processor to the control_slave port of the system ID peripheral. For more information about the system ID peripheral, refer to the System ID Core... - Page 25 Chapter 1: Nios II Hardware Development 1–21 Creating the Design Example 1. On the Component Library tab, expand Peripherals, expand Microcontroller Peripherals, and then click PIO (Parallel I/O). 2. Click Add. The PIO (Parallel I/O) parameter editor appears. Figure 1–11 shows the GUI.

-

Page 26: Specify Base Addresses And Interrupt Request Priorities

7. Connect the clk_reset port of the clk_0 clock source to the reset port of the PIO. 8. Connect the data_master port of the Nios II processor to the s1 port of the PIO. 9. In the external_connection row, click Click to export in the Export column to export the PIO ports. -

Page 27: Generate The Qsys System

Chapter 1: Nios II Hardware Development 1–23 Creating the Design Example 5. Click the IRQ value for the sys_clk_timer component to select it. 6. Type 1 and press Enter to assign a new IRQ value. Figure 1–12 shows the Qsys System Contents tab with the complete system. -

Page 28: Integrate The Qsys System Into The Quartus Ii Project

6. On the File menu, click Exit to close Qsys and return to the Quartus II software. Congratulations! You have finished creating the Nios II processor system. You are ready to integrate the system into the Quartus II hardware project and use the Nios II SBT for Eclipse to develop software. -

Page 29: Instantiate The Qsys System Module In The Quartus Ii Project

6. Click to anchor the symbol in place. 7. If your target board does not have LEDs that the Nios II system can drive, you must delete the LEDG[7..0] pins. To delete the pins, perform the following steps: a. Click the output symbol LEDG[7..0] to select it. -

Page 30: Add Ip Variation File

You must know the pin layout for the board to complete this section. You also must know other requirements for using the board, which are beyond the scope of this document. Refer to the documentation for your board. For Altera development board reference manuals, refer to the Literature: Development Kits page of the Altera website. - Page 31 Chapter 1: Nios II Hardware Development 1–27 Creating the Design Example 2. In the Family list, select the FPGA family that matches your board. If prompted to remove location assignments, do so. 3. Under Target device, select Specific device selected in 'Available devices' list.

- Page 32 1–28 Chapter 1: Nios II Hardware Development Creating the Design Example 5. In the PLD_CLOCKINPUT row, double-click in the Location cell to access a list of available pin locations. Figure 1–16 shows the GUI. Figure 1–16. Assigning Pins with the Quartus II Pin Planner 6.

-

Page 33: Compile The Quartus Ii Project And Verify Timing

Chapter 1: Nios II Hardware Development 1–29 Creating the Design Example Figure 1–17 shows the Unused Pins page of the Device and Pin Options dialog box. Figure 1–17. The Unused Pins Page of the Device and Pin Options Dialog Box 14. - Page 34 1–30 Chapter 1: Nios II Hardware Development Creating the Design Example To ensure the design meets timing, perform the following steps: 1. On the File menu, click Open. 2. In the Files of type list, select Script Files (*.tcl, *.sdc, *.qip).

- Page 35 Volume 1: Design and Synthesis of the Quartus II Handbook. Congratulations! You have finished integrating the Nios II system into the Quartus II project. You are ready to download the .sof to the target board. Download the Hardware Design to the Target FPGA In this section you download the .sof to the target board.

-

Page 36: Develop Software Using The Nios Ii Sbt For Eclipse

7. Click Start. The Progress meter sweeps to 100% as the Quartus II software configures the FPGA. At this point, the Nios II system is configured and running in the FPGA, but it does not yet have a program in memory to execute. - Page 37 Chapter 1: Nios II Hardware Development 1–33 Creating the Design Example 4. On the File menu, point to New, and then click Nios II Application and BSP from Template. The Nios II Application and BSP from Template wizard appears. Figure 1–20 shows the GUI.

-

Page 38: Compile The Project

Perform the following steps: 1. In the Project Explorer view, right-click count_binary_bsp and click Properties. The Properties for count_binary_bsp dialog box appears. 2. Click the Nios II BSP Properties page. The Nios II BSP Properties page contains basic software build settings. Figure 1–21 shows the GUI. -

Page 39: Run The Program On Target Hardware

1–24, then the LEDs blink in a binary counting pattern. 2. Click the Terminate icon (the red square) on the toolbar of the Nios II Console view to terminate the run session. When you click the Terminate icon, the Nios II SBT for Eclipse disconnects from the target hardware. -

Page 40: Taking The Next Step

Getting Started with the Graphical User ■ Interface chapter of the Nios II Software Developer’s Handbook—This tutorial teaches in detail how to use the Nios II SBT for Eclipse to develop, run, and debug new Nios II C/C++ application projects. ■ Nios II Processor Reference Handbook—This handbook provides complete reference... -

Page 41: Additional Information

Date Version Changes May 2011 Revised entire document to use Qsys. December 2009 Revised entire document to use Nios II Software Build Tools for Eclipse. Added altera.components project information. ■ October 2007 Minor text changes. ■ Updated to describe new SOPC Builder MegaWizard design flow. -

Page 42: Typographic Conventions

A warning calls attention to a condition or possible situation that can cause you injury. The envelope links to the Email Subscription Management Center page of the Altera website, where you can sign up to receive update notifications for Altera documents. Nios II Hardware Development Tutorial May 2011 Altera Corporation...

Need help?

Do you have a question about the Nios II and is the answer not in the manual?

Questions and answers