Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for United Electronic Industries DNA-IRIG-650

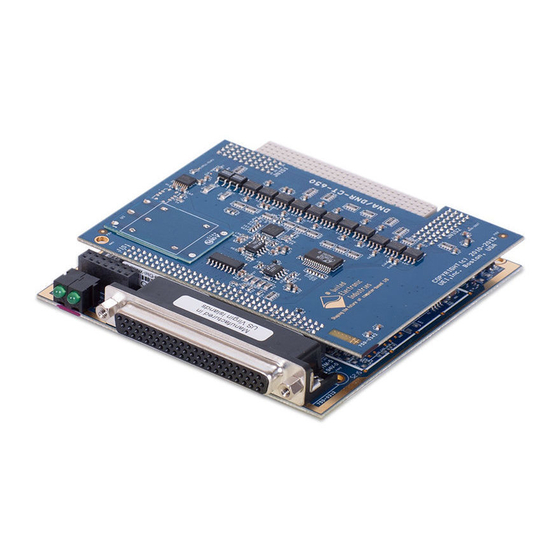

- Page 1 DNA/DNR-IRIG-650 — User Manual IRIG-A, B, E and G Timing Generation and Synchronization board for the PowerDNA Cube and PowerDNR RACKtangle Release 4.6 March 2019 PN Man-DNx-IRIG-650-319 © Copyright 1998-2019 United Electronic Industries, Inc. All rights reserved.

- Page 2 COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS. Products sold by United Electronic Industries, Inc. are not authorized for use as critical components in life support devices or systems. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

-

Page 3: Table Of Contents

Custom PLL frequency generation ....... . 48 Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650-ManualTOC.fm... - Page 4 Pinout for the DNx-IRIG-650 series layer ..............9 Pinout, photo, and schema of DNA-CBL-650 accessory ..........50 Photo of DNA-ACC-650 break-out board and BNC-650..........51 Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650-ManualLOF.fm...

-

Page 5: Chapter 1 Introduction

Introduction Chapter 1 Introduction This document outlines the feature set and use of the DNR- and DNA-IRIG-650 layer. The IRIG-650 Timing Generation and Synchronization board is a module for the UEI PowerDNA I/O Cube (DNA-IRIG-650) and the DNR-1G HalfRACK and RACKtangle chassis (DNR-IRIG-650). The DNR version is electronically identical to the DNA version except that the DNR version is designed to plug into a RACKtangle backplane instead of a Cube chassis. -

Page 6: Introduction

The term DNR is a specific reference to the RACKtangle, DNA to the PowerDNA I/O Cube, and DNx to refer to both. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap1x.fm... -

Page 7: Layer Features

1MHz, 5 MHz, 10 MHz (TTL-OutX, SYNCx) • Custom PLL frequency (1Hz -1 MHz, 4 digits accurate) • 1 PPS, 1 PPM, 1PPM (TTL-OutX, SYNCx) • Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap1x.fm... -

Page 8: Technical Specification

50 g, 3 ms half sine, 18 shocks @ 6 orientations 30 g, 11 ms half sine, 18 shocks @ 6 orientations Altitude to 70,000 feet Table 1-1. Technical Specifications Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap1x.fm... -

Page 9: Indicators

AM Output AM Output Circuitry On-Board Output FPGA Drivers Logic Level Outputs Antenna Interface Programmable Figure 1-1. Simplified Block Diagram of the IRIG-650 Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap1x.fm... -

Page 10: Functional Diagram Of Dnx-Irig-650 Board

20 MHz Aux D/A -- ±50ppb Input CL FIFO clock fine tuning initial accuracy Figure 1-2. Functional Diagram of DNx-IRIG-650 board Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap1x.fm... -

Page 11: Introduction

±500ppb, the majority of which will happen within the first year of operation and can be compensated by the in-factory calibration which uses a Rubidium Standard source. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap1x.fm... -

Page 12: Introduction

(2MHz max), designed to adjust its period to a 1PPS source from the TimeKeeper or from a TTL input. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap1x.fm... -

Page 13: Layer Connectors And Wiring

DNA-STP-37 screw terminal panel or other panel. Please note that 12 of these signals are twisted pairs with their respective grounds as shown in the appendix. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap1x.fm... -

Page 14: Chapter 2 Programming With The High Level Api

The following sample code shows how to configure the time keeper channel of Input a IRIG-650 set as device 1: // Configure the time keeper CUeiIRIGTimeKeeperChannel* pTKChannel = irigSession.CreateIRIGTimeKeeperChannel( "pdna://192.168.100.2/Dev1/Irig0", UeiIRIG1PPSInternal, autoFollow); Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap2x.fm... - Page 15 (it measures and averages number of base clock cycles between externally derived 1PPS pulses when they are valid). // enable nominal value pTKChannel->EnableNominalValue(true); Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap2x.fm...

-

Page 16: Irig Output

Start when input is valid: If selected, the output time coder waits for • the input time decoder to receive a valid time code before starting. // start when input is valid pOutChan->EnableStartWhenInputValid(true); Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap2x.fm... -

Page 17: Irig Input

Single P0 Marker: Determines whether to use only one marker P0 in • the timing byte stream. // Enable single P0 marker pInChan->EnableSingleP0Marker(true); Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap2x.fm... -

Page 18: Gps Input

– UeiIRIGDOTTLPrecision1MHZ: Precision 1MHz – UeiIRIGDOTTLNRZStartStrobe: Output NRZ start strobe – UeiIRIGDOTTLManchesterIITimeCode: Manchester II output time code – UeiIRIGDOTTLNRZTimeCode: NRZ output time code Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap2x.fm... -

Page 19: Configuring The Timing

In simple mode, the delay between reads is determined by software on the host computer. The following sample shows how to configure the simple mode. // configure timing irigSsession.ConfigureTimingForSimpleIO(); Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap2x.fm... -

Page 20: Reading Data

To reuse the object with a different set of channels or parameters, the Session you can manually clean up the session as follows: // clean up the session irigSession.CleanUp(); Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap2x.fm... -

Page 21: Chapter 3 Programming With The Low Level Api

The code samples are self-explanatory, however this section elaborates the more complicated details with step-by-step descriptions that provide insight into the behavior behind the examples. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm... -

Page 22: Low-Level Functions

DqAdv650GetTimeANSI Sets time in binary format. DqAdv650SetTimeSBS Sets time in ANSI/System V format. DqAdv650SetTimeANSI Writes data into the GPS module serial interface. DqAdv650WriteGPS Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm... -

Page 23: Time Keeper Programming

2. Flag CT650_TKFLG_USENOMINAL allows user to select whether to use nominal period (i.e. 100E6 pulses of 100MHz base clock) or the measured Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm... - Page 24 IRIG codes with sub-PPS frame rates. For IRIG-B 0x700 code normal, for sub-PPS and high frame rate codes, 1PPS invalid warnings might be set. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 25 – year is valid CT650_TIME_TM_YEAR – day of the year is valid CT650_TIME_TM_YDAY to specify what part of the supplied time is valid. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 26 // TRUE if CF codes are present int is_sbs; // TRUE if SBS is present int is_year; //TRUE if CF chars 50-58 have BCD year data } CT650_IRIG_PRM_DEF, *pCT650_IRIG_PRM_DEF; Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 27 = (pCT650_IRIG_PRM_DEF)malloc(sizeof(CT650_IRIG_PRM_DEF)); memcpy(pOutPrm, pPrmDef, sizeof(CT650_IRIG_PRM_DEF)); pOutPrm->is_sbs = FALSE; // supress SBS in output ret = DqAdv650SetTimecodeOutput(hd, devn, mode, output, pOutPrm, pDataDef); Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 28 { CT650_VAL_01,BCD_SEC_b(6),BCD_SEC_r(6),BCD_SEC_d(6)}, // == BCD minutes: == // position 9 { CT650_VAL_P, BCD_NoP_b(), BCD_NoP_r(), BCD_NoP_d()}, // position 10 unit minutes { CT650_VAL_01,BCD_MIN_b(0),BCD_MIN_r(0),BCD_MIN_d(0)}, … Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 29 ((2))// No operation for CF section #define SBS_SEC_r(B) // SBS seconds register #define CF_NoP_r() // No operation for CF section #define SBS_NoP_r() // No operation for SBS section Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 30 (0 == (i%10)) printf("."); switch (tcode) { case 0: printf("i"); break; case 1: printf("P"); break; case 2: printf("0"); break; case 3: printf("1"); break; } Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 31 This function can override calculated setting made by the firmware. It needs to be called after DqAdv650SetTimecodeInput() with the CT650_IN_DISABLED flag, but before enabling layer input with DqAdv650Enable() . Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 32 // ct650_l1_max - maximum number of // pulses in level 1 position // system-defined part uint32 cr_tol_min; // ct650_cr_tol_min (signal // tolerance - MAN2 mode only) Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 33 // Zero crossing "High"("Mark") amplitude minimum #define CT650_ZC_MMIN 0x2094 // Zero crossing "Low"("Space") amplitude maximum #define CT650_ZC_SMAX 0x2098 // Zero crossing "Low"("Space") amplitude minimum #define CT650_ZC_SMIN 0x209C Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 34 "logic 0" gain [0..2] <low_gain> adjusts DC output offset [-0.5..+0.5] <offset> The default high-to-low ratio is 3:1 with zero offset and 2V amplitude. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 35 CT650_OUT_CFG_MII_NRZ - Event 3 (on event: 60µs or 1ms pulse) CT650_OUT_CFG_EVENT3 - Event 2 CT650_OUT_CFG_EVENT2 - Event 1 CT650_OUT_CFG_EVENT1 - Event 0 CT650_OUT_CFG_EVENT0 Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 36 The current state of SYNC line can be routed to any TTL Out line using one of the CT650_OUT_CFG_SRC_SYNCx constants. NOTE: Make sure that no two layers actively are driving the same SYNC line simultaneously. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 37 In the latter case, user should call ret = DqAdv650Enable(hd, DEVN, TRUE); to enable initialized subsystems together, and ret = DqAdv650Enable(hd, DEVN, FALSE); to disable them. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 38 The structure values are described on the following pages. Notice that the same fields can have a different meaning based on the <event_cfg> mode of operation. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 39 DNA/DNR-IRIG-650 IRIG Timing Layer Chapter 3 Programming with the Low Level API Table 3-1. Event Registers Summary Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 40 Specify the active edge of the event source, for event CT650_EVT_CFG_EDGE sources 8-31. Set to 1 for event sources 1-7. Event source mode (0 to 31). See next two tables, below CT650_EVT_CFG_ESRC_... Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 41 External TTL input 1 CT650_EVT_TTL1 External TTL input 2 CT650_EVT_TTL2 External TTL input 3 CT650_EVT_TTL3 External TTL input 4 CT650_EVT_TTL4 28-31 Reserved. RSVD Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 42 ESRC=EVT_CFG_ESRC_DNAB - DNA bus data • when ESRC=EVT_CFG_ESRC_SBT - straight binary day of the year (and • SB microseconds) when ESRC=EVT_CFG_ESRC_BCDT - microseconds • Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 43 =1-if event is armed by the start trigger (or start trigger is CT650_EVT_STS_SEARM unused) =1-if subevent 1 counter is active CT650_EVT_STS_SEVT1 =1-if subevent 0 counter is active CT650_EVT_STS_SEVT0 Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 44 To disable an event, call DqAdv650SetEvents() for that channel with a nulled <event> structure (e.g. set all <event> structure fields to 0). Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 45 // Set event to send event packet with when time is decoded and ready to view (1PPS for IRIG-B) ret = DqAdv650ConfigEvents(async_hd, DEVN, evt_chan_rdy, 0, EV650_TIMERDY, NULL); Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 46 // If we start receiving time re-enable error messages if (reenable_errors) ret = DqAdv650ConfigEvents(handle- >handle, DEVN, CT650_EVENT_CHERR, DQEVENT_ONCE, EV650_ERROR, &error_mask); reenable_errors = FALSE; break; Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 47 • CT650_TKSTS – time decoder status • CT650_TDSTS – time generator status • CT650_SWG_STS Please see meaning of these status bits in powerdna.h. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 48 UTC time of the fix. hh = hours mm = minutes ss = seconds $GPGGA,hhmmss.dd,xxmm.dddd,<N|S> dd = decimal part of seconds ,yyymm.dddd,<E|W>,v,ss,d.d,h.h,M ,g.g,M,a.a,xxxx*hh<CR><LF> hhmmss.dd Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 49 Letter denoting direction of magnetic variation. Either E = East <E|W> or W = West. Not supported Mode indicator A=autonomous N=data not valid Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 50 Mode: 1 = Fix not available, 2 = 2D, 3 = 3D ID (PRN) numbers of GPS satellites used in solution PDOP HDOP VDOP Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 51 Command Number: Three byte character string. From “ 000 ” to “ 999 ” An identifier used to tell the decoder how to decode the command Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 52 By configuring the custom PLL generation as seen above, and then configuring a SYNC line as seen in Section 3.2.4 for either: CT650_OUT_CFG_SRC_CR (for logics before 0x010210D8) • Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

- Page 53 ClockIn(hd, LAYER_TO_BE_CLOCKED, DQ_EXT_SYNCx) and configuring the layer to use this input source instead, it is possible to clock the layer from a IRIG-650 PLL. Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 Chap3x.fm...

-

Page 54: Pinout, Photo, And Schema Of Dna-Cbl-650 Accessory

ISGND 13 32 TTL-OUT2 ISGND 14 34 TTL-OUT3 ISGND 16 ISGND 17 ISGND 18 Figure A-1. Pinout, photo, and schema of DNA-CBL-650 accessory Tel: 508-921-4600 www.ueidaq.com Vers: 4.6 © Copyright 2019 United Electronic Industries, Inc. Date: March 2019 DNx-IRIG-650 AppxX.fm... -

Page 55: Photo Of Dna-Acc-650 Break-Out Board And Bnc-650

DNA/DNR-IRIG-650 IRIG Timing Layer DNA-ACC-650 Break-out board connects to DNA-IRIG-650 primary 62-pin connector and pro- vides GPS, AM-IN, AM-OUT and EXTCLK-IN to mini-BNC connectors. DNA-BNC-650 Cable for DNA-ACC-650’s mini-BNC connector to BNC for external devices; 1ft long. Figure A-2. Photo of DNA-ACC-650 break-out board and BNC-650 Tel: 508-921-4600 www.ueidaq.com... -

Page 56: Copyright

//ftp.ueidaq.com ii Support Web Site High Level API www.ueidaq.com Tel: 508-921-4600 Tel: 508-921-4600 www.ueidaq.com www.ueidaq.com Vers: 4.6 Vers: 4.6 © Copyright 2019 © Copyright 2019 United Electronic Industries, Inc. United Electronic Industries, Inc. Date: March 2019 Date: March 2019 DNx-IRIG-650-ManualIX.fm DNx-IRIG-650-ManualIX.fm...

Need help?

Do you have a question about the DNA-IRIG-650 and is the answer not in the manual?

Questions and answers