Summary of Contents for Xilinx Spartan-3E

- Page 1 Spartan-3E Starter Kit Board User Guide Click a component to jump to the related documentation. Not all UG230 (v1.0) March 9, 2006 components have active links.

-

Page 2: Revision History

Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design. -

Page 3: Table Of Contents

....... . . 11 Spartan-3E FPGA Features and Embedded Processing Functions ....11 Learning Xilinx FPGA, CPLD, and ISE Development Software Basics . - Page 4 ..........51 Display Configuration www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

- Page 5 Disable Other Devices on the SPI Bus to Avoid Contention ....79 Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006...

- Page 6 Xilinx XC2C64A CPLD ........

-

Page 7: Rs-232 Ports, Vga Port, And Ps/2 Port

..........148 Spartan-3E Starter Kit Board User Guide www.xilinx.com... - Page 8 ..... 154 DDR SDRAM Series Termination and FX2 Connector Differential Termination Appendix B: Example User Constraints File (UCF) www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 9: Preface: About This Guide

VHDL or Verilog source code, please visit the following web link. • Spartan™-3E Starter Kit Board Reference Page http://www.xilinx.com/s3estarter Acknowledgements Xilinx wishes to thank the following companies for their support of the Spartan-3E Starter Kit board: • Intel Corporation for the 128 Mbit StrataFlash memory •... -

Page 10: Additional Resources

SHA-1 secure EEPROM for authenticating or copy-protecting FPGA configuration bitstreams. • Appendix A, “Schematics,” lists the schematics for the Spartan-3E Starter Kit board. • Appendix B, “Example User Constraints File (UCF),” provides example code from a UCF. -

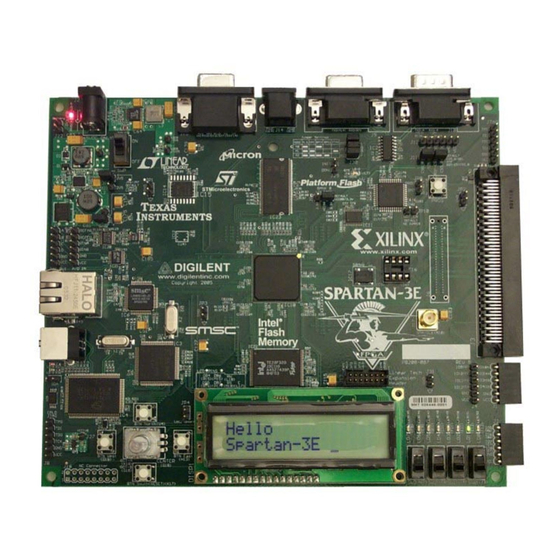

Page 11: Chapter 1: Introduction And Overview

Chapter 1 Introduction and Overview Thank you for purchasing the Xilinx Spartan™-3E Starter Kit. You will find it useful in developing your Spartan-3E FPGA application. Choose the Starter Kit Board for Your Needs Depending on specific requirements, choose the Xilinx development board that best suits your needs. -

Page 12: Key Components And Features

Also consider the capable boards offered by Xilinx partners: • Spartan-3 and Spartan-3E Board Interactive Search http://www.xilinx.com/products/devboards/index.htm Key Components and Features The key features of the Spartan-3E Starter Kit board are: • Xilinx XC3S500E Spartan-3E FPGA ♦ Up to 232 user-I/O pins ♦... -

Page 13: Design Trade-Offs

• 8-pin DIP socket for auxiliary clock oscillator Design Trade-Offs A few system-level design trade-offs were required in order to provide the Spartan-3E Starter Kit board with the most functionality. Configuration Methods Galore! A typical FPGA application uses a single non-volatile memory to store configuration images. - Page 14 Chapter 1: Introduction and Overview www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 15: Chapter 2: Switches, Buttons, And Knob

Switches, Buttons, and Knob Slide Switches Locations and Labels The Spartan-3E Starter Kit board has four slide switches, as shown in Figure 2-1. The slide switches are located in the lower right corner of the board and are labeled SW3 through SW0. -

Page 16: Push-Button Switches

Figure 2-2: UCF Constraints for Slide Switches Push-Button Switches Locations and Labels The Spartan-3E Starter Kit board has four momentary-contact push-button switches, shown in Figure 2-3. The push buttons are located in the lower left corner of the board and are labeled BTN_NORTH, BTN_EAST, BTN_SOUTH, and BTN_WEST. -

Page 17: Ucf Location Constraints

2-6. Use an internal pull-down resistor within the FPGA pin to generate a logic Low. Figure 2-9 shows how to specify a pull-down resistor within the UCF. There is no active debouncing circuitry on the push button. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... -

Page 18: Rotary Shaft Encoder

As shown in Figure 2-8, the chatter can falsely indicate extra rotation events or even indicate rotations in the opposite www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 19: Ucf Location Constraints

Figure 2-9: UCF Constraints for Rotary Push-Button Switch Discrete LEDs Locations and Labels The Spartan-3E Starter Kit board has eight individual surface-mount LEDs located above the slide switches as shown in Figure 2-10. The LEDs are labeled LED7 through LED0. -

Page 20: Operation

Operation Each LED has one side connected to ground and the other side connected to a pin on the Spartan-3E device via a 390Ω current limiting resistor. To light an individual LED, drive the associated FPGA control signal High. UCF Location Constraints... -

Page 21: Chapter 3: Clock Sources

As shown in Figure 3-1, the Spartan-3E Starter Kit board supports three primary clock input sources, all of which are located below the Xilinx logo, near the Spartan-3E logo. • The board includes an on-board 50 MHz clock oscillator. •... -

Page 22: Clock Connections

I/O pin assignment and the I/O standard used. The settings assume that jumper JP9 is set for 3.3V. If JP9 is set for 2.5V, adjust the IOSTANDARD settings accordingly. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 23: Clock Period Constraints

= LVCMOS33 ; Figure 3-2: UCF Location Constraints for Clock Sources Clock Period Constraints The Xilinx ISE development software uses timing-driven logic placement and routing. Set the clock PERIOD constraint as appropriate. An example constraint appears in Figure 3-3 for the on-board 50 MHz clock oscillator. The CLK_50MHZ frequency is 50 MHz, which equates to a 20 ns period. - Page 24 Chapter 3: Clock Sources www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 25: Chapter 4: Fpga Configuration Options

The Spartan-3E Starter Kit board supports a variety of FPGA configuration options: • Download FPGA designs directly to the Spartan-3E FPGA via JTAG, using the on- board USB interface. The on-board USB-JTAG logic also provides in-system programming for the on-board Platform Flash PROM and the Xilinx XC2C64A CPLD. -

Page 26: Configuration Mode Jumpers

The DONE pin LED lights when the FPGA successfully finishes configuration. Pressing the PROG button forces the FPGA to restart its configuration process. The 4 Mbit Xilinx Platform Flash PROM provides easy, JTAG-programmable configuration storage for the FPGA. The FPGA configures from the Platform Flash using Master Serial mode. -

Page 27: Prog Push Button

PROG Push Button Table 4-1: Spartan-3E Configuration Mode Jumper Settings (Header J30 in Figure 4-2) Configuration Mode Pins Mode M2:M1:M0 FPGA Configuration Image Source Jumper Settings Master Serial 0:0:0 Platform Flash PROM 1:1:0 SPI Serial Flash PROM starting at address 0... -

Page 28: Programming The Fpga, Cpld, Or Platform Flash Prom Via Usb

Figure 4-3: Standard USB Type A/Type B Cable The wider and narrower Type A connector fits the USB connector at the back of the computer. After installing the Xilinx software, connect the square Type B connector to the Spartan-3E Starter Kit board, as shown in Figure 4-4. -

Page 29: Programming Via Impact

JTAG programming file, as shown in Figure 4-6. If not already prompted, click the first device in the chain, the Spartan-3E FPGA, to highlight it. Right-click the FPGA and select Assign New Configuration File. Select the desired FPGA configuration file and click OK. - Page 30 PC’s USB port and the iMPACT settings. UG230_c4_09_022406 Figure 4-8: Right-Click to Program the Spartan-3E FPGA When the FPGA successfully programs, the iMPACT software indicates success, as shown Figure 4-9.

-

Page 31: Programming Platform Flash Prom Via Usb

CCLK oscillator always starts at its slowest setting, approximately 1.5 MHz. Most external PROMs support a higher frequency. Increase the CCLK frequency as appropriate to reduce the FPGA’s configuration time. The Xilinx XCF04S Platform Flash supports a 25 MHz CCLK frequency. - Page 32 Rate drop list, choose 25 to increase the internal CCLK oscillator to approximately 25 MHz, the fastest frequency when using an XCF04S Platform Flash PROM. Click OK when finished. UG230_c4_12_022706 Figure 4-11: Set CCLK Configuration Rate under Configuration Options www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 33: Generating The Prom File

Figure 4-13. UG230_c4_14_022706 Figure 4-13: Double-Click Generate PROM, ACE, or JTAG File After iMPACT starts, double-click PROM File Formatter, as shown in Figure 4-14. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... - Page 34 Chapter 4: FPGA Configuration Options UG230_c4_15_022706 Figure 4-14: Double-Click PROM File Formatter Choose Xilinx PROM as the target PROM type, as shown in Figure 4-15. Select from any of the PROM File Formats; the Intel Hex format (MCS) is popular. Enter the Location of the directory and the PROM File Name.

- Page 35 Programming the FPGA, CPLD, or Platform Flash PROM via USB The Spartan-3E Starter Kit board has an XCF04S Platform Flash PROM. Select xcf04s from the drop list, as shown in Figure 4-16. Click Add, then click Next >. UG230_c4_17_022706 Figure 4-16: Choose the XCF04S Platform Flash PROM...

- Page 36 Figure 4-19 shows an example for a single XC3S500E FPGA bitstream stored in an XCF04S Platform Flash PROM. UG230_c4_20_022706 Figure 4-19: PROM Formatting Completed www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 37: Programming The Platform Flash Prom

Place the iMPACT software in the JTAG Boundary Scan mode, either by choosing Boundary Scan in the iMPACT Modes pane, as shown in Figure 4-22, or by clicking on the Boundary Scan tab. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... - Page 38 Select a previously generated PROM format file and click OK. UG230_c4_24_022806 Figure 4-23: Assign the PROM File to the XCF04S Platform Flash PROM To start programming the PROM, right-click the PROM icon and then click Program.. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

- Page 39 The Load FPGA option immediately forces the FPGA to reconfigure after programming the Platform Flash PROM. The FPGA’s configuration mode pins must be set for Master Serial mode, as defined in Table 4-1, page 27. Click OK when finished. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006...

- Page 40 FPGA to reconfigure from the newly programmed Platform Flash PROM. If the FPGA successfully configures, the DONE LED, also shown in Figure 4-2, lights up. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 41: Chapter 5: Character Lcd Screen

Chapter 5 Character LCD Screen Overview The Spartan-3E Starter Kit board prominently features a 2-line by 16-character liquid crystal display (LCD). The FPGA controls the LCD via the 4-bit data interface shown in Figure 5-1. Although the LCD supports an 8-bit data interface, the Starter Kit board uses a 4-bit data interface to remain compatible with other Xilinx development boards and to minimize total pin count. -

Page 42: Character Lcd Interface Signals

StrataFlash in byte-wide (x8) mode. Upper data lines are not used. Full access to both LCD and StrataFlash. Notes: 1. ‘X’ indicates a don’t care, can be either 0 or 1. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 43: Ucf Location Constraints

0x00 and 0x0F. The second line of characters is stored between addresses 0x40 and 0x4F. Undisplayed Character Display Addresses Addresses … … … Figure 5-3: DD RAM Hexadecimal Addresses (No Display Shifting) Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... -

Page 44: Cg Rom

DB[3:0] = “0011” binary. As shown in Figure 5-4, the character ‘S’ appears on the screen. English/Roman characters are stored in CG ROM at their equivalent ASCII code address. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 45: Cg Ram

CG RAM. Write CG RAM data using the Write Data to CG RAM or DD RAM command, and read CG RAM using the Read Data from CG RAM or DD RAM command. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... -

Page 46: Command Set

The upper nibble is transferred first, followed by the lower nibble. Table 5-3: LCD Character Display Command Set Upper Nibble Lower Nibble Function Clear Display Return Cursor Home Entry Mode Set Display On/Off Cursor and Display Shift www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 47: Disabled

These operations are performed during data reads and writes. Execution Time: 40 μs Bit DB1: (I/D) Increment/Decrement Auto-decrement address counter. Cursor/blink moves to left. Auto-increment address counter. Cursor/blink moves to right. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... -

Page 48: Display On/Off

When the displayed data is shifted repeatedly, both lines move horizontally. The second display line does not shift into the first display line. Execution Time: 40 μs www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 49: Function Set

Write data into DD RAM if the command follows a previous Set DD RAM Address command, or write data into CG RAM if the command follows a previous Set CG RAM Address command. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... -

Page 50: Read Data From Cg Ram Or Dd Ram

LCD_E 230 ns 40 ns 10 ns Upper Lower 4 bits 4 bits LCD_RS SF_D[11:8] LCD_RW LCD_E 1 μs 40 μs UG230_c5_03_022006 Figure 5-6: Character LCD Interface Timing www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 51: Transferring 8-Bit Data Over The 4-Bit Interface

0x06, to set the display to automatically increment the address pointer. • Issue a Display On/Off command, 0x0C, to turn the display on and disables the cursor and blinking. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... -

Page 52: Writing Data To The Display

Also drive the LCD_RW pin Low to prevent the LCD screen from presenting data. Related Resources • Initial Design for Spartan-3E Starter Kit (Reference Design) http://www.xilinx.com/s3estarter • PowerTip PC1602-D Character LCD (Basic Electrical and Mechanical Data) http://www.powertipusa.com/pdf/pc1602d.pdf •... -

Page 53: Chapter 6: Vga Display Port

UG230_c6_01_021706 Figure 6-1: VGA Connections from Spartan-3E Starter Kit Board The Spartan-3E FPGA directly drives the five VGA signals via resistors. Each color line has a series resistor, with one bit each for VGA_RED, VGA_GREEN, and VGA_BLUE. The series resistor, in combination with the 75Ω termination built into the VGA cable, ensures that the color signals remain in the VGA-specified 0V to 0.7V range. -

Page 54: Signal Timing For A 60 Hz, 640X480 Vga Display

Much of the potential display time is therefore lost in blanking periods when the beam is reset and stabilized to begin a new horizontal or vertical display pass. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... - Page 55 Video data typically comes from a video refresh memory with one or more bytes assigned to each pixel location. The Spartan-3E Starter Kit board uses three bits per pixel, producing one of the eight possible colors shown in Table 6-1.

-

Page 56: Vga Signal Timing

No time relationship is specified between the onset of the HS pulse and the onset of the VS pulse. Consequently, the counters can be arranged to easily form video RAM addresses, or to minimize decoding logic for sync pulse generation. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 57: Ucf Location Constraints

= LVTTL | DRIVE = 8 | SLEW = FAST ; Figure 6-4: UCF Constraints for VGA Display Port Related Resources • VESA http://www.vesa.org • VGA timing information http://www.epanorama.net/documents/pc/vga_timing.html Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... - Page 58 Chapter 6: VGA Display Port www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 59: Overview

As shown in Figure 7-1, the Spartan-3E Starter Kit board has two RS-232 serial ports: a female DB9 DCE connector and a male DTE connector. The DCE-style port connects directly to the serial port connector available on most personal computers and workstations via a standard straight-through serial cable. -

Page 60: Ucf Location Constraints

= LVTTL ; NET "RS232_DCE_TXD" = "M14" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = SLOW ; Figure 7-3: UCF Location Constraints for DCE RS-232 Serial Port www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 61: Chapter 8: Ps/2 Mouse/Keyboard Port

Both a PC mouse and keyboard use the two-wire PS/2 serial bus to communicate with a host device, the Spartan-3E FPGA in this case. The PS/2 bus includes both clock and data. Both a mouse and keyboard drive the bus with identical signal timings and both use 11-bit words that include a start, stop and odd parity bit. -

Page 62: Keyboard

Some keys, called extended keys, send an “E0” ahead of the scan code and furthermore, they might send more than one scan code. When an extended key is released, an “E0 F0” key-up code is sent, followed by the scan code. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... - Page 63 When the keyboard sends data, it generates 11 clock transitions at around 20 to 30 kHz, and data is valid on the falling edge of the clock as shown in Figure 8-2. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006...

-

Page 64: Mouse

50 ms or so. The L and R fields in the status byte indicate Left and Right button presses. A ‘1’ indicates that the associated mouse button is being pressed. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 65: Voltage Supply

Voltage Supply Voltage Supply The PS/2 port on the Spartan-3E Starter Kit board is powered by 5V. Although the Spartan-3E FPGA is not a 5V-tolerant device, it can communicate with a 5V device using series current-limiting resistors, as shown in Figure 8-1. - Page 66 Chapter 8: PS/2 Mouse/Keyboard Port www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 67: Chapter 9: Digital To Analog Converter (Dac)

Chapter 9 Digital to Analog Converter (DAC) The Spartan-3E Starter Kit board includes an SPI-compatible, four-channel, serial Digital- to-Analog Converter (DAC). The DAC device is a Linear Technology LTC2624 quad DAC with 12-bit unsigned resolution. The four outputs from the DAC appear on the J5 header,... -

Page 68: Interface Signals

Although the StrataFlash PROM is a parallel device, its least-significant data bit is shared with the SPI_MISO signal. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 69: Spi Communication Details

DAC, the previous 32-bit command word is echoed back to the master. The response from the DAC can be ignored although it is a useful to confirm correct communication. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... -

Page 70: Specifying The Dac Output Voltage

DAC outputs A and B. The reference voltage associated with DAC outputs A and B is 2.5V ± 5%. D 11:0 × ± -------------------- - 2.5V 5% Equation 9-3 OUTC 4096 www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 71: Ucf Location Constraints

= 8 ; Figure 9-5: UCF Location Constraints for the DAC Interface Related Resources • LTC2624 Quad DAC Data Sheet http://www.linear.com/pc/downloadDocument.do?navId=H0,C1,C1155,C1005,C1156,P2048,D2170 • PicoBlaze Based D/A Converter Control for the Spartan-3E Starter Kit (Reference Design) http://www.xilinx.com/s3estarter • Xilinx PicoBlaze Soft Processor http://www.xilinx.com/picoblaze •... - Page 72 Chapter 9: Digital to Analog Converter (DAC) www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 73: Chapter 10: Analog Capture Circuit

Chapter 10 Analog Capture Circuit The Spartan-3E Starter Kit board includes a two-channel analog capture circuit, consisting of a programmable scaling pre-amplifier and an analog-to-digital converter (ADC), as shown in Figure 10-1. Analog inputs are supplied on the J7 header. -

Page 74: Digital Outputs From Analog Inputs

VINA or VINB. The maximum range of the ADC is ±1.25V, centered around the reference voltage, 1.65V. Hence, 1.25V appears in the denominator to scale the analog input accordingly. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 75: Programmable Pre-Amplifier

The gain of each amplifier is programmable from -1 to -100, as shown in Table 10-2. Table 10-2: Programmable Gain Settings for Pre-Amplifier Input Voltage Range Gain Minimum Maximum 1.025 2.275 Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... -

Page 76: Spi Control Interface

SPI_MOSI (from FPGA) 85 max AMP_DOUT Previous 7 (from AMP) All timing is minimum in nanoseconds unless otherwise noted. UG230_c10_04_022306 Figure 10-4: SPI Timing When Communicating with Amplifier www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 77: Ucf Location Constraints

The maxim sample rate is approximately 1.5 MHz. The ADC presents the digital representation of the sampled analog values as a 14-bit, two’s complement binary value. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... -

Page 78: Ucf Location Constraints

= LVCMOS33 | SLEW = SLOW | DRIVE = 8 ; "SPI_MISO" = "N10" | IOSTANDARD = LVCMOS33 ; Figure 10-8: UCF Location Constraints for the ADC Interface www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 79: Disable Other Devices On The Spi Bus To Avoid Contention

Platform Flash PROM Connecting Analog Inputs Connect AC signals to VINA or VINB via a DC blocking capacitor. Related Resources • Amplifier and A/D Converter Control for the Spartan-3E Starter Kit (Reference Design) http://www.xilinx.com/s3estarter • Xilinx PicoBlaze Soft Processor http://www.xilinx.com/picoblaze •... - Page 80 Chapter 10: Analog Capture Circuit www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 81: Chapter 11: Intel Strataflash Parallel Nor Flash Prom

PROM As shown in Figure 11-1, the Spartan-3E Starter Kit boards includes a 128 Mbit (16 Mbyte) Intel StrataFlash parallel NOR Flash PROM. As indicated, some of the StrataFlash connections are shared with other components on the board. Intel StrataFlash... -

Page 82: Strataflash Connections

Although the XC3S500E FPGA only requires just slightly over 2 Mbits per configuration image, the FPGA-to-StrataFlash interface on the board support up to a 256 Mbit StrataFlash. The Spartan-3E Starter Kit board ships with a 128 Mbit device. Address line SF_A24 is not used. - Page 83 Connects to FPGA pins A[19:0] to support the BPI configuration. SF_A18 SF_A17 SF_A16 SF_A15 SF_A14 SF_A13 SF_A12 SF_A11 SF_A10 SF_A9 SF_A8 SF_A7 SF_A6 SF_A5 SF_A4 SF_A3 SF_A2 SF_A1 SF_A0 Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006...

- Page 84 StrataFlash Byte Enable. Connects to FPGA pin LDC2 to support the BPI configuration. 0: x8 data 1: x16 data SF_STS StrataFlash Status signal. Connects to FPGA user-I/O pin. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 85: Shared Connections

The FPGA accesses the StrataFlash PROM. Xilinx XC2C64A CPLD The Xilinx XC2C64A CoolRunner CPLD controls the five upper StrataFlash address lines, SF_A<24:20> during configuration. The four upper BPI-mode address lines from the FPGA, A<23:20> are not connected. Instead, four FPGA user-I/O pins connect to the StrataFlash PROM upper address lines SF_A<23:0>. -

Page 86: Ucf Location Constraints

= SLOW ; "SPI_MISO" = "N10" | IOSTANDARD = LVCMOS33 | DRIVE = 6 | SLEW = SLOW ; Figure 11-3: UCF Location Constraints for StrataFlash Data I/Os www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 87: Control

A[24:20] during BPI configuration. Related Resources • Intel J3 StrataFlash Data Sheet http://www.intel.com/design/flcomp/products/j3/techdocs.htm#datasheets • ® Application Note 827, Intel StrataFlash Memory (J3) to Xilinx Spartan-3E FPGA Design Guide http://www.intel.com/design/flcomp/applnots/307257.htm Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... - Page 88 Chapter 11: Intel StrataFlash Parallel NOR Flash PROM www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 89: Chapter 12: Spi Serial Flash

Chapter 12 SPI Serial Flash The Spartan-3E Starter Kit board includes a STMicroelectronics M25P16 16 Mbit SPI serial Flash, useful in a variety of applications. The SPI Flash provides an alternative means to configure the FPGA—a new feature of Spartan-3E FPGAs as shown in Figure 12-1. -

Page 90: Configuring From Spi Flash

Set the FPGA configuration mode pins for SPI mode, as shown in Figure 12-4. The location of the configuration mode jumpers (J30) appears in Figure 12-3. UG230_c15_03_030206 Figure 12-4: Set Mode Pins for SPI Mode www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 91: Creating An Spi Serial Flash Prom File

Regenerate the FPGA bitstream programming file with the new settings. UG230_c15_04_030206 Figure 12-5: Set Configuration Rate to 12 MHz When Using the M25P16 SPI Flash Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... -

Page 92: Formatting An Spi Flash Prom File

Formatter automatically swaps the bit direction as SPI Flash PROMs shift out the most- significant bit (MSB) first. Enter the Location of the directory and the PROM File Name. Click Next > when finished. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... - Page 93 Configuring from SPI Flash UG230_c15_07_030206 Figure 12-8: Choose the PROM Target Type, the, Data Format, and File Location The Spartan-3E Starter Kit board has a 16 Mbit SPI serial Flash PROM. Select 16M from the drop list, as shown in Figure 12-9.

- Page 94 PROM, the select FPGA bitstream(s), and the amount of PROM space consumed by the bitstream. Figure 12-12 shows an example for a single XC3S500E FPGA bitstream stored in an XCF04S Platform Flash PROM. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

- Page 95 The PROM Formatter creates an output file based on the settings shown in Figure 12-8. In this example, the output file is called MySPIFlash.mcs. UG230_c15_13_030206 Figure 12-14: PROM File Formatter Succeeded Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006...

-

Page 96: Downloading The Design To Spi Flash

Xilinx Parallel Cable IV with flying leads • Digilent JTAG3 programming cable These cables are not provided with the Spartan-3E Starter Kit board but can be purchased separately, either from the Xilinx Online Store or from Digilent, Inc. (see “Related Resources,” page 102). -

Page 97: Insert Jumper On Jp8 And Hold Prog_B Low

Jumper Installed: FPGA Held in Configuration State, I/Os in High Impedance UG230_c15_15_030206 Figure 12-16: Installing the JP8 Jumper Holds the FPGA in Configuration State Re-apply power to the Spartan-3E Starter Kit board. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... -

Page 98: Programming The Spi Flash With The Xspi Software

Figure 12-16a. If properly programmed, the FPGA then configures itself from the SPI Flash PROM and the DONE LED lights. The DONE LED is shown in Figure 12-3. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 99: Additional Design Details

Figure 12-18: Additional SPI Flash Interface Design Details Shared SPI Bus with Peripherals After configuration, the SPI Flash configuration pins are available to the application. On the Spartan-3E Starter Kit board, the SPI bus is shared by other SPI-capable peripheral devices, as shown in Figure 12-18. -

Page 100: Other Spi Flash Control Signals

In SPI configuration mode, the FPGA selects the attached SPI Flash by asserting the CSO_B pin Low. On the Spartan-3E Starter Kit board, the CSO_B pin drives into the jumper J11 block. This jumper block provides the option to move the on-board SPI Flash to a different select line (SPI_ALT_CS_JP11). - Page 101 Pin 1: 16-pin SOIC Pin 1: 8-pin SOIC (Do not connect) 8-lead MLP HOLD (Do not connect) UG230_c15_18_030606 Figure 12-19: Multi-Package Layout for the STMicroelectronics M25Pxx Family Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006...

-

Page 102: Related Resources

M25Pxx in Your Application http://www.st.com/stonline/products/literature/an/9540.pdf • PicoBlaze SPI Serial Flash Programmer, via RS-232 (Reference Design) http://www.xilinx.com/s3estarter • Using Serial Flash on the Spartan-3E Starter Kit Board (Reference Design) http://www.xilinx.com/s3estarter • Universal Scan SPI Flash Programming via JTAG Training Video http://www.ricreations.com/JTAG-Software-Downloads.htm www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 103: Chapter 13: Ddr Sdram

Chapter 13 DDR SDRAM The Spartan-3E Starter Kit boards includes a 512 Mbit (32M x 16) Micron Technology DDR SDRAM (MT46V32M16) with a 16-bit data interface, as shown in Figure 13-1. All DDR SDRAM interface pins connect to the FPGA’s I/O Bank 3 on the FPGA. I/O Bank 3 and the DDR SDRAM are both powered by 2.5V, generated by an LTC3412 regulator from the... -

Page 104: Ddr Sdram Connections

Table 13-1: FPGA-to-DDR SDRAM Connections DDR SDRAM FPGA Pin Category Signal Name Number Function SD_A12 Address inputs SD_A11 SD_A10 SD_A9 SD_A8 SD_A7 SD_A6 SD_A5 SD_A4 SD_A3 SD_A2 SD_A1 SD_A0 www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... - Page 105 Data Mask. Upper and Lower data masks SD_LDM SD_UDQS Data Strobe. Upper and Lower data strobes SD_LDQS SD_CK_FB SDRAM clock feedback into top DCM within FPGA. Used by some DDR SDRAM controller cores Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006...

-

Page 106: Ucf Location Constraints

= SSTL2_I ; "SD_DQ<1>" = "L1" | IOSTANDARD = SSTL2_I ; "SD_DQ<0>" = "L2" | IOSTANDARD = SSTL2_I ; Figure 13-3: UCF Location Constraints for DDR SDRAM Data I/Os www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 107: Control

• Xilinx Embedded Design Kit (EDK) http://www.xilinx.com/ise/embedded_design_prod/platform_studio.htm • MT46V32M16 (32M x 16) DDR SDRAM Data Sheet http://download.micron.com/pdf/datasheets/dram/ddr/512MBDDRx4x8x16.pdf • MicroBlaze OPB Double Data Rate (DDR) SDRAM Controller (v2.00b) http://www.xilinx.com/bvdocs/ipcenter/data_sheet/opb_ddr.pdf Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... - Page 108 Chapter 13: DDR SDRAM www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

- Page 109 Chapter 14 10/100 Ethernet Physical Layer Interface The Spartan-3E Starter Kit board includes a Standard Microsystems LAN83C185 10/100 Ethernet physical layer (PHY) interface and an RJ-45 connector, as shown in Figure 14-1. With an Ethernet Media Access Controller (MAC) implemented in the FPGA, the board can optionally connect to a standard Ethernet network.

-

Page 110: Chapter 14: 10/100 Ethernet Physical Layer Interface

Transmit Enable. E_TX_CLK Transmit Clock. 25 MHz in 100Base-TX mode, and 2.5 MHz in 10Base-T mode. E_RXD<4> Receive Data from PHY. E_RXD<3> E_RXD<2> E_RXD<1> E_RXD<0> E_RX_DV Receive Data Valid. www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 111: Microblaze Ethernet Ip Cores

UG230_c14_03_022706 Figure 14-3: Ethernet MAC IP Cores for the Spartan-3E Starter Kit Board The Ethernet MAC core requires design constraints to meet the required performance. Refer to the OPB Ethernet MAC data sheet (v1.02) for details. The OPB bus clock frequency must be 65 MHz or higher for 100 Mbps Ethernet operations and 6.5 MHz or faster for... -

Page 112: Ucf Location Constraints

Chapter 14: 10/100 Ethernet Physical Layer Interface The hardware evaluation versions of the Ethernet MAC cores operate for approximately eight hours in silicon before timing out. To order the full version of the core, visit the Xilinx website at: http://www.xilinx.com/ipcenter/processor_central/processor_ip/10-100emac/ 10-100emac_order_register.htm... -

Page 113: Chapter 15: Expansion Connectors

Chapter 15 Expansion Connectors The Spartan-3E Starter Kit board provides a variety of expansion connectors for easy interface flexibility to other off-board components. The board includes the following I/O expansion headers (see Figure 15-1): • A Hirose 100-pin edge connector with 43 associated FPGA user-I/O pins, including up to 15 differential LVDS I/O pairs and two Input-only pairs •... -

Page 114: Voltage Supplies To The Connector

Three signals are reserved primarily as clock signals between the board and FX2 connector, although all three connect to full I/O pins. Voltage Supplies to the Connector The Spartan-3E Starter Kit board provides power to the Hirose 100-pin FX connector and any attached board via two supplies (see Figure 15-2). - Page 115 FX2_IO2 FX2_IO3 FX2_IO4 FX2_IO5 FX2_IO6 FX2_IO7 FX2_IO8 FX2_IO9 FX2_IO10 FX2_IO11 FX2_IO12 FX2_IO13 FX2_IO14 FX2_IO15 FX2_IO16 FX2_IO17 FX2_IO18 FX2_IO19 FX2_IO20 FX2_IO21 FX2_IO22 FX2_IO23 FX2_IO24 FX2_IO25 FX2_IO26 FX2_IO27 FX2_IO28 FX2_IO29 Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006...

-

Page 116: Compatible Board

FX2_CLKIO 5.0V 5.0V 5.0V SHIELD Compatible Board The following board is compatible with the FX2 connector on the Spartan-3E Starter Kit board: • VDEC1 Video Decoder Board from Digilent, Inc. http://www.digilentinc.com/Products/Detail.cfm?Prod=VDEC1 Mating Receptacle Connectors The Spartan-3E Starter Kit board uses a Hirose FX2-100P-1.27DS header connector. The header mates with any compatible 100-pin receptacle connector, including board-mounted and non-locking cable connectors. - Page 117 FX2_IO26 IO_L03P_0 FX2_IO27 IO_L01N_0 R207 FX2_IO28 IO_L01P_0 FX2_IP35 IP_L07N_0 Input R208 FX2_IP36 IP_L07P_0 Input FX2_IP37 IP_L02N_0 Input R209 FX2_IP38 IP_L02P_0 Input IO_L11N_0/ FX2_CLKIN GCLK5 R210 IO_L11P_0/ FX2_CLKOUT GCLK4 Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006...

-

Page 118: Using Differential Inputs

15 and 16. The second option, shown in Figure 15-3b, is a Spartan-3E feature called on-chip differential termination, which uses the DIFF_TERM attribute available on differential I/O signals. Each differential I/O pin includes a circuit that behaves like an internal termination resistor of approximately 120Ω... -

Page 119: Using Differential Outputs

I/O standard used, assuming that all connections use single-ended I/O standards. These header connections are shared with the 6-pin accessory headers, as shown in Figure 15-11, page 122. Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... - Page 120 DRIVE = 8 ; "FX2_IP<40>" = "C15" | IOSTANDARD = LVCMOS33 | SLEW = FAST | DRIVE = 8 ; Figure 15-7: UCF Location Constraints for Accessory Headers www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 121: Six-Pin Accessory Headers

The board supplies 3.3V to the accessory board mounted in the J2 socket on the bottom pin. Spartan-3E FPGA FX2_IO5 (A6) FX2_IO6 (B6) FX2_IO7 (E7) FX2_IO8 (F7) 3.3V UG230_c12_08_022406 Figure 15-9: FPGA Connections to the J2 Accessory Header Spartan-3E Starter Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006... -

Page 122: Header J4

= SLOW DRIVE = 6 ; #NET "J4<3>" = "E8" | IOSTANDARD = LVTTL SLEW = SLOW DRIVE = 6 ; Figure 15-11: UCF Location Constraints for Accessory Headers www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 123: Connectorless Debugging Port Landing Pads (J6)

Agilent, provides an interface to a logic analyzer. This debugging port is intended primarily for the Xilinx ChipScope Pro software with the Agilent’s FPGA Dynamic Probe. It can, however, be used with either the Agilent or Tektronix probes, without the ChipScope software, using FPGA Editor’s probe command. -

Page 124: Related Resources

Agilent B4655A FPGA Dynamic Probe for Logic Analyzer http://www.home.agilent.com/USeng/nav/-536898189.536883660/pd.html?cmpid=92641 • Agilent 5404A/6A Pro Series Soft Touch Connector http://www.home.agilent.com/cgi-bin/pub/agilent/Product/cp_Product.jsp?NAV_ID=-536898227.0.00 • Tektronix P69xx Probe Module s with D-Max Technology http://www.tek.com/products/accessories/logic_analyzers/p6800_p6900.html www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 125: Chapter 16: Xc2C64A Coolrunner-Ii Cpld

Chapter 16 XC2C64A CoolRunner-II CPLD The Spartan-3E Starter Kit board includes a Xilinx XC2C64A CoolRunner-II CPLD. The CPLD is user programmable and available for customer applications. Portions of the CPLD are reserved to coordinate behavior between the various FPGA configuration memories, namely the Xilinx Platform Flash PROM and the Intel StrataFlash PROM. - Page 126 Intel StrataFlash SF_A<21> (V13) (P20) SF_A<20> (T12) (P19) A[23:20] A[24:20] SF_A<19:0> A[19:0] A[19:0] A[23:20] Unconnected UG230_c16_01_030906 Figure 16-1: XC2C64A CoolRunner-II CPLD Controls Master Serial and BPI Configuration Modes www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

-

Page 127: Ucf Location Constraints

UCF Location Constraints UCF Location Constraints – There are two sets of constraints listed below one for the Spartan-3E FPGA and one for the XC2C64A CoolRunner-II CPLD. FPGA Connections to CPLD Figure 16-2 provides the UCF constraints for the FPGA connections to the CPLD , including the I/O pin assignment and the I/O standard used. -

Page 128: Related Resources

Chapter 16: XC2C64A CoolRunner-II CPLD Related Resources • CoolRunner-II CPLD Family Data Sheet http://direct.xilinx.com/bvdocs/publications/ds090.pdf • XC2C64A CoolRunner-II CPLD Data Sheet http://direct.xilinx.com/bvdocs/publications/ds311.pdf • Default XC2C64A CPLD Design for Spartan-3E Starter Kit Board http://www.xilinx.com/s3estarter www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 129: Chapter 17: Ds2432 1-Wire Sha-1 Eeprom

Chapter 17 DS2432 1-Wire SHA-1 EEPROM The Spartan-3E Starter Kit board includes a Maxim DS2432 serial EEPROM with an integrated SHA-1 engine. As shown in Figure 17-1, the DS2432 EEPROM uses the Maxim 1-Wire interface, which as the name implies, cleverly uses a single wire for power and serial communication. - Page 130 Chapter 17: DS2432 1-Wire SHA-1 EEPROM www.xilinx.com Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006...

- Page 131 “Intel StrataFlash Parallel NOR Flash Memory and Micron DDR SDRAM ” • “Buttons, Switches, Rotary Encoder, and Character LCD ” • “DDR SDRAM Series Termination and FX2 Connector Differential Termination” Spartan-3E Start Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006...

-

Page 132: Appendix A: Schematics

Header J7 provides the two analog inputs to the programmable pre-amplifier (AMP) and two-channel Analog-to-Digital Converter (ADC). The diagram in the lower left corner shows the JTAG chain. Chapter 15, “Expansion Connectors,” for additional information. www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 134: Rs-232 Ports, Vga Port, And Ps/2 Port

The SMA connector allows an external clock source to drive one of the FPGA’s global clock inputs. Alternatively, the FPGA can provide a high-performance clock to another board via the SMA connector. See Chapter 3, “Clock Sources,” for additional information. www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 136: Ethernet Phy, Magnetics, And Rj-11 Connector

Ethernet MAC implemented within the FPGA. J19 is the RJ-11 Ethernet connector associated with the 10/100 Ethernet PHY. Chapter 14, “10/100 Ethernet Physical Layer Interface,” for additional information. www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 138: Voltage Regulators

Resistors R65 and R67 create a voltage divider to create the termination voltage required for the DDR SDRAM interface. IC9 is a 1.8V supply to the Embedded USB download/debug circuit and to the CPLD’s VCCINT supply input. www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 140: Fpga Configurations Settings, Platform Flash Prom, Spi Serial Flash, Jtag Connections

IC14 and IC15 are alternate landing pads for the STMicro SPI serial Flash. IC14 accepts the 16-pin SOIC package option, while IC15 accepts either the 8-pin SOIC or MLP package option. See Figure 12-19, page 101 for additional informaton. www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 142: Fpga I/O Banks 0 And 1, Oscillators

IC17 is the 50 MHz clock oscillator. Chapter 3, “Clock Sources,” for additional information. IC16 is an 8-pin DIP socket to insert an alternate clock oscillator with a different frequency. www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 144: Fpga I/O Banks 2 And 3

IC10B3 represents the connections to I/O Bank 3 on the FPGA. Bank 3 is dedicated to the DDR SDRAM interface and is consequently powered by 2.5V. See Chapter 13, “DDR SDRAM,” for additional information. www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 146: Power Supply Decoupling

Jumper JP9 defines the voltage applied to VCCO on I/O Bank 0. The default setting is 3.3V. “Voltage Control,” page 22 “Voltage Supplies to the Connector,” page 114 additional details. www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 148: Xc2C64A Coolrunner-Ii Cpld

Appendix A: Schematics XC2C64A CoolRunner-II CPLD IC18 is a Xilinx XC2C64A CoolRunner-II CPLD. The CPLD primarily provides additional flexibility when configuring the FPGA from parallel NOR Flash and during MultiBoot configurations. When the CPLD is loaded with the appropriate design, JP10 enables a watchdog timer in the CPLD used during fail-safe MultiBoot configurations. -

Page 150: Linear Technology Adc And Dac

LTC6912 programmable pre-amplifier (AMP) to condition the analog inputs to the ADC. Chapter 10, “Analog Capture Circuit,” for additional information. IC21 is a Linear Technology LTC2624 four-channel DAC. See Chapter 9, “Digital to Analog Converter (DAC),” for additional information. www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 152: Intel Strataflash Parallel Nor Flash Memory And Micron Ddr Sdram

Chapter 11, “Intel StrataFlash Parallel NOR Flash PROM,” for additional information. IC23 is a 512 Mbit (64 Mbyte) Micron DDR SDRAM. See Chapter 13, “DDR SDRAM,” additional information. www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 154: Buttons, Switches, Rotary Encoder, And Character Lcd

LD0 through LD7 are discrete LEDs. Chapter 2, “Switches, Buttons, and Knob,” for additional information. DISP1 is a 2x16 character LCD screen. See Chapter 5, “Character LCD Screen,” additional information. www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006... -

Page 156: Ddr Sdram Series Termination And Fx2 Connector Differential Termination

Resistors R202 through R210 are not loaded on the board. These landing pads provide optional connections for 100Ω differential termination resistors. See “Using Differential Inputs,” page 118 for additional information. www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006... - Page 158 Appendix A: Schematics www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006...

- Page 159 Appendix B Example User Constraints File (UCF) ##################################################### ### SPARTAN-3E STARTER KIT BOARD CONSTRAINTS FILE ##################################################### # ==== Analog-to-Digital Converter (ADC) ==== some connections shared with SPI Flash, DAC, ADC, and AMP NET "AD_CONV" LOC = "P11" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 6 ;...

- Page 160 NET "FX2_IO<25>" LOC = "C14" | IOSTANDARD = LVCMOS33 | SLEW = FAST | DRIVE = 8 ; NET "FX2_IO<26>" LOC = "D14" | IOSTANDARD = LVCMOS33 | SLEW = FAST | DRIVE = 8 ; www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006...

- Page 161 LOC = "C11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ; NET "LED<5>" LOC = "D11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ; Spartan-3E Start Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006...

- Page 162 NET "SD_DQ<13>" LOC = "G5" | IOSTANDARD = SSTL2_I ; NET "SD_DQ<14>" LOC = "H6" | IOSTANDARD = SSTL2_I ; NET "SD_DQ<15>" LOC = "H5" | IOSTANDARD = SSTL2_I ; www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006...

- Page 163 | IOSTANDARD = LVCMOS33 | DRIVE = 4 | SLEW = SLOW ; NET "SF_D<15>" LOC = "T8" | IOSTANDARD = LVCMOS33 | DRIVE = 4 | SLEW = SLOW ; Spartan-3E Start Kit Board User Guide www.xilinx.com UG230 (v1.0) March 9, 2006...

- Page 164 LOC = "H16" | IOSTANDARD = LVCMOS33 | DRIVE = 4 | SLEW = SLOW ; NET "GCLK10" LOC = "C9" | IOSTANDARD = LVCMOS33 | DRIVE = 4 | SLEW = SLOW ; www.xilinx.com Spartan-3E Start Kit Board User Guide UG230 (v1.0) March 9, 2006...

Need help?

Do you have a question about the Spartan-3E and is the answer not in the manual?

Questions and answers