Table of Contents

Advertisement

Quick Links

Features

•

High-performance, Low-power AVR

•

Advanced RISC Architecture

– 133 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers + Peripheral Control Registers

– Fully Static Operation

– Up to 16 MIPS Throughput at 16 MHz

– On-chip 2-cycle Multiplier

•

High Endurance Non-volatile Memory segments

– 128K Bytes of In-System Self-programmable Flash program memory

– 4K Bytes EEPROM

– 4K Bytes Internal SRAM

– Write/Erase cycles: 10,000 Flash/100,000 EEPROM

– Data retention: 20 years at 85°C/100 years at 25°C

– Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

True Read-While-Write Operation

– Up to 64K Bytes Optional External Memory Space

– Programming Lock for Software Security

– SPI Interface for In-System Programming

•

JTAG (IEEE std. 1149.1 Compliant) Interface

– Boundary-scan Capabilities According to the JTAG Standard

– Extensive On-chip Debug Support

– Programming of Flash, EEPROM, Fuses and Lock Bits through the JTAG Interface

•

Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

– Two Expanded 16-bit Timer/Counters with Separate Prescaler, Compare Mode and

Capture Mode

– Real Time Counter with Separate Oscillator

– Two 8-bit PWM Channels

– 6 PWM Channels with Programmable Resolution from 2 to 16 Bits

– Output Compare Modulator

– 8-channel, 10-bit ADC

8 Single-ended Channels

7 Differential Channels

2 Differential Channels with Programmable Gain at 1x, 10x, or 200x

– Byte-oriented Two-wire Serial Interface

– Dual Programmable Serial USARTs

– Master/Slave SPI Serial Interface

– Programmable Watchdog Timer with On-chip Oscillator

– On-chip Analog Comparator

•

Special Microcontroller Features

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated RC Oscillator

– External and Internal Interrupt Sources

– Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby, and

Extended Standby

– Software Selectable Clock Frequency

– ATmega103 Compatibility Mode Selected by a Fuse

– Global Pull-up Disable

•

I/O and Packages

– 53 Programmable I/O Lines

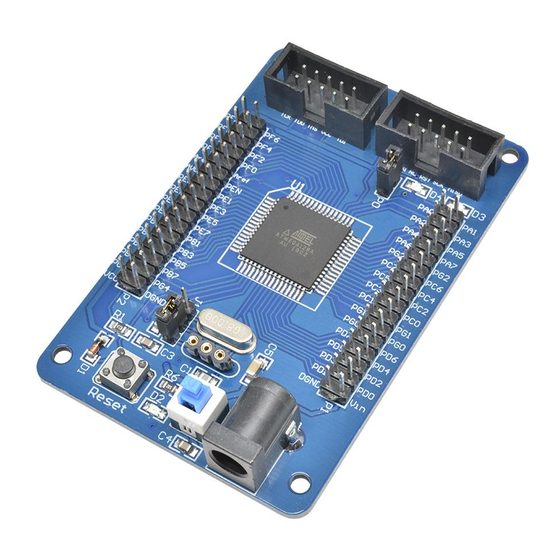

– 64-lead TQFP and 64-pad QFN/MLF

•

Operating Voltages

– 2.7 - 5.5V ATmega128L

– 4.5 - 5.5V ATmega128

•

– 0 - 8 MHz ATmega128L

– 0 - 16 MHz ATmega128

®

8-bit Microcontroller

(1)

8-bit

Microcontroller

with 128K Bytes

In-System

Programmable

Flash

ATmega128

ATmega128L

Note:

Not recommended for new

designs.

Rev. 2467S–AVR–07/09

Advertisement

Table of Contents

Summary of Contents for Atmel ATmega128

- Page 1 – 64-lead TQFP and 64-pad QFN/MLF Note: Not recommended for new • Operating Voltages designs. – 2.7 - 5.5V ATmega128L – 4.5 - 5.5V ATmega128 • Speed Grades – 0 - 8 MHz ATmega128L – 0 - 16 MHz ATmega128 Rev. 2467S–AVR–07/09...

- Page 2 Overview The ATmega128 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega128 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

- Page 3 ATmega128 Block Diagram Figure 2. Block Diagram PF0 - PF7 PA0 - PA7 PC0 - PC7 PORTA DRIVERS PORTF DRIVERS PORTC DRIVERS DATA REGISTER DATA DIR. DATA REGISTER DATA DIR. DATA REGISTER DATA DIR. PORTF REG. PORTF PORTA REG. PORTA PORTC REG.

- Page 4 Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega128 is a powerful microcontroller that provides a highly flexible and cost effec- tive solution to many embedded control applications.

- Page 5 External Interrupt pins 3 - 0 serve as level interrupt only. • USART has no FIFO buffer, so data overrun comes earlier. Unused I/O bits in ATmega103 should be written to 0 to ensure same operation in ATmega128. Pin Descriptions Digital supply voltage.

- Page 6 Note: The ATmega128 is by default shipped in ATmega103 compatibility mode. Thus, if the parts are not programmed before they are put on the PCB, PORTC will be output during first power up, and until the ATmega103 compatibility mode is disabled.

- Page 7 ATmega128 RESET Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 19 on page 51. Shorter pulses are not guaranteed to generate a reset.

- Page 8 Resources A comprehensive set of development tools, application notes, and datasheets are available for download on http://www.atmel.com/avr. ATmega128/L rev. A - M characterization is found in the ATmega128 Appendix A. Note: Data Retention Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C.

- Page 9 ATmega128 About Code This datasheet contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compi- Examples lation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent.

- Page 10 The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed in the ALU. After an arithmetic opera- tion, the Status Register is updated to reflect information about the result of the operation. ATmega128 2467S–AVR–07/09...

- Page 11 The I/O memory space contains 64 addresses which can be accessed directly, or as the Data Space locations following those of the Register file, $20 - $5F. In addition, the ATmega128 has Extended I/O space from $60 - $FF in SRAM where only the ST/STS/STD and LD/LDS/LDD instructions can be used.

- Page 12 • Two 8-bit output operands and one 16-bit result input • One 16-bit output operand and one 16-bit result input Figure 4 on page 13 shows the structure of the 32 general purpose working registers in the CPU. ATmega128 2467S–AVR–07/09...

- Page 13 ATmega128 Figure 4. AVR CPU General Purpose Working Registers Addr. … General Purpose Working Registers … X-register Low Byte X-register High Byte Y-register Low Byte Y-register High Byte Z-register Low Byte Z-register High Byte Most of the instructions operating on the Register file have direct access to all registers, and most of them are single cycle instructions.

- Page 14 The RAMPZ Register is normally used to select which 64K RAM Page is accessed by the Z- pointer. As the ATmega128 does not support more than 64K of SRAM memory, this register is used only to select which page in the program memory is accessed when the ELPM/SPM instruction is used.

- Page 15 ATmega128 Figure 6 shows the parallel instruction fetches and instruction executions enabled by the Har- vard architecture and the fast-access Register file concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

- Page 16 = SREG; /* store SREG value */ /* disable interrupts during timed sequence */ __disable_interrupt(); EECR |= (1<<EEMWE); /* start EEPROM write */ EECR |= (1<<EEWE); SREG = cSREG; /* restore SREG value (I-bit) */ ATmega128 2467S–AVR–07/09...

- Page 17 ATmega128 When using the SEI instruction to enable interrupts, the instruction following SEI will be exe- cuted before any pending interrupts, as shown in this example. Assembly Code Example ; set global interrupt enable sleep; enter sleep, waiting for interrupt ;...

- Page 18 This section describes the different memories in the ATmega128. The AVR architecture has two main memory spaces, the Data Memory and the Program Memory space. In addition, the ATmega128 ATmega128 features an EEPROM Memory for data storage. All three memory spaces are linear Memories and regular.

- Page 19 64 location reserved in the Opcode for the IN and OUT instructions. For the Extended I/O space from $60 - $FF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used. The Extended I/O space does not exist when the ATmega128 is in the ATmega103 com- patibility mode.

- Page 20 X, Y, and Z are decremented or incremented. The 32 general purpose working registers, 64 I/O registers, and the 4096 bytes of internal data SRAM in the ATmega128 are all accessible through all these addressing modes. The Register file is described in “General Purpose Register File”...

- Page 21 Memory access instruction Next instruction EEPROM Data The ATmega128 contains 4K bytes of data EEPROM memory. It is organized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at Memory least 100,000 write/erase cycles.

- Page 22 Initial Value • Bits 7..4 – Res: Reserved Bits These bits are reserved bits in the ATmega128 and will always read as zero. • Bit 3 – EERIE: EEPROM Ready Interrupt Enable Writing EERIE to one enables the EEPROM Ready Interrupt if the I-bit in SREG is set. Writing EERIE to zero disables the interrupt.

- Page 23 ATmega128 The EEPROM can not be programmed during a CPU write to the Flash memory. The software must check that the Flash programming is completed before initiating a new EEPROM write. Step 2 is only relevant if the software contains a boot loader allowing the CPU to program the Flash.

- Page 24 & (1<<EEWE)) /* Set up address and data registers */ EEAR = uiAddress; EEDR = ucData; /* Write logical one to EEMWE */ EECR |= (1<<EEMWE); /* Start eeprom write by setting EEWE */ EECR |= (1<<EEWE); ATmega128 2467S–AVR–07/09...

- Page 25 ATmega128 The next code examples show assembly and C functions for reading the EEPROM. The exam- ples assume that interrupts are controlled so that no interrupts will occur during execution of these functions. Assembly Code Example EEPROM_read: ; Wait for completion of previous write...

- Page 26 “Register Summary” on page 362. All ATmega128 I/Os and peripherals are placed in the I/O space. All I/O locations may be accessed by the LD/LDS/LDD and ST/STS/STD instructions, transferring data between the 32 general purpose working registers and the I/O space. I/O registers within the address range $00 - $1F are directly bit-accessible using the SBI and CBI instructions.

- Page 27 SRW11 SRW10 0xFFFF 0xFFFF Note: ATmega128 in non ATmega103 compatibility mode: Memory Configuration A is available (Memory Configuration B N/A) ATmega128 in ATmega103 compatibility mode: Memory Configuration B is available (Memory Configuration A N/A) ATmega103 Both External Memory Control Registers (XMCRA and XMCRB) are placed in Extended I/O Compatibility space.

- Page 28 G low (t ) must not exceed address valid to ALE low (t ) minus PCB AVLLC wiring delay (dependent on the capacitive load). Figure 12. External SRAM Connected to the AVR D[7:0] AD7:0 A[7:0] SRAM A[15:8] A15:8 ATmega128 2467S–AVR–07/09...

- Page 29 The most important parameters are the access time for the external memory compared to the set-up requirement of the ATmega128. The access time for the External Memory is defined to be the time from receiving the chip select/address until the data of this address actually is driven on the bus.

- Page 30 1. SRWn1 = SRW11 (upper sector) or SRW01 (lower sector), SRWn0 = SRW10 (upper sector) or SRW00 (lower sector). The ALE pulse in period T6 is only present if the next instruction accesses the RAM (internal or external). ATmega128 2467S–AVR–07/09...

- Page 31 ATmega128 Figure 16. External Data Memory Cycles with SRWn1 = 1 and SRWn0 = 1 System Clock (CLK A15:8 Prev. addr. Address DA7:0 Prev. data Address Data DA7:0 (XMBK = 0) Prev. data Address Data DA7:0 (XMBK = 1) Prev. data...

- Page 32 13 through Figures 16 for how the setting of the SRW bits affects the timing. • Bit 0 – Res: Reserved Bit This is a reserved bit and will always read as zero. When writing to this address location, write this bit to zero for compatibility with future devices. ATmega128 2467S–AVR–07/09...

- Page 33 ATmega128 External Memory Control Register B – XMCRB XMBK – – – – XMM2 XMM1 XMM0 XMCRB Read/Write Initial Value • Bit 7– XMBK: External Memory Bus-keeper Enable Writing XMBK to one enables the bus keeper on the AD7:0 lines. When the bus keeper is enabled, it will ensure a defined logic level (zero or one) on AD7:0 when they would otherwise be tri-stated.

- Page 34 AVR Memory Map External 32K SRAM 0x0000 0x0000 0x0000 0x0000 Internal Memory Internal Memory 0x0FFF 0x0FFF 0x1000 0x1000 0x10FF 0x10FF 0x1100 0x1100 External External 0x7FFF 0x7FFF 0x7FFF 0x7FFF 0x8000 Memory 0x8000 Memory 0x90FF 0x8FFF 0x9100 0x9000 (Unused) (Unused) 0xFFFF 0xFFFF ATmega128 2467S–AVR–07/09...

- Page 35 ATmega128 Using all 64KB Since the External Memory is mapped after the Internal Memory as shown in Figure 11, only Locations of External 60KB of External Memory is available by default (address space 0x0000 to 0x10FF is reserved Memory for internal memory). However, it is possible to take advantage of the entire External Memory by masking the higher address bits to zero.

- Page 36 TWI address reception in all sleep modes. Flash Clock – clk The Flash clock controls operation of the Flash interface. The Flash clock is usually active simul- FLASH taneously with the CPU clock. ATmega128 2467S–AVR–07/09...

- Page 37 ATmega128 Asynchronous Timer The Asynchronous Timer clock allows the Asynchronous Timer/Counter to be clocked directly Clock – clk from an external 32 kHz clock crystal. The dedicated clock domain allows using this Timer/Counter as a real-time counter even when the device is in sleep mode.

- Page 38 The device is shipped with CKSEL = “0001” and SUT = “10”. The default clock source setting is therefore the Internal RC Oscillator with longest startup time. This default setting ensures that all Source users can make their desired clock source setting using an In-System or Parallel Programmer. ATmega128 2467S–AVR–07/09...

- Page 39 ATmega128 Crystal Oscillator XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be con- figured for use as an On-chip Oscillator, as shown in Figure 19. Either a quartz crystal or a ceramic resonator may be used. The CKOPT fuse selects between two different Oscillator Amplifier modes.

- Page 40 Fast rising power or BOD enabled 1K CK 65 ms Slowly rising power 32K CK 65 ms Stable frequency at start-up Reserved Note: 1. These options should only be used if frequency stability at start-up is not important for the application. ATmega128 2467S–AVR–07/09...

- Page 41 ATmega128 External RC For timing insensitive applications, the External RC configuration shown in Figure 20 can be Oscillator used. The frequency is roughly estimated by the equation f = 1/(3RC). C should be at least 22 pF. By programming the CKOPT fuse, the user can enable an internal 36 pF capacitor between XTAL1 and GND, thereby removing the need for an external capacitor.

- Page 42 RC Oscillator. At 5V, 25°C and 1.0 MHz Oscillator frequency selected, this calibration gives a frequency within ± 3% of the nominal frequency. Using calibration methods as described in application notes available at www.atmel.com/avr it is possible to achieve ± 1% accuracy at any given V and Temperature.

- Page 43 ATmega128 to the register gives the highest available frequency. The calibrated Oscillator is used to time EEPROM and Flash access. If EEPROM or Flash is written, do not calibrate to more than 10% above the nominal frequency. Otherwise, the EEPROM or Flash write may fail. Note that the Oscillator is intended for calibration to 1.0, 2.0, 4.0, or 8.0 MHz.

- Page 44 32.768 kHz watch crystal. Applying an external clock source to TOSC1 is not recommended. Note: The Timer/Counter Oscillator uses the same type of crystal oscillator as Low-Frequency Oscillator and the internal capacitors have the same nominal value of 36 pF. ATmega128 2467S–AVR–07/09...

- Page 45 MCU wakes up and executes from the Reset Vector. Figure 18 on page 36 presents the different clock systems in the ATmega128, and their distribu- tion. The figure is helpful in selecting an appropriate sleep mode. MCU Control Register The MCU Control Register contains control bits for power management.

- Page 46 Power-save mode because the contents of the registers in the asynchronous timer should be considered undefined after wake-up in Power-save mode if AS0 is 0. This sleep mode basically halts all clocks except clk , allowing operation only of asynchronous modules, including Timer/Counter0 if clocked asynchronously. ATmega128 2467S–AVR–07/09...

- Page 47 ATmega128 Standby Mode When the SM2..0 bits are 110 and an External Crystal/Resonator clock option is selected, the SLEEP instruction makes the MCU enter Standby mode. This mode is identical to Power-down with the exception that the Oscillator is kept running. From Standby mode, the device wakes up in 6 clock cycles.

- Page 48 “Digital Input Enable and Sleep Modes” on page 70 details on which pins are enabled. If the input buffer is enabled and the input signal is left floating or have an analog signal level close to V /2, the input buffer will use excessive power. ATmega128 2467S–AVR–07/09...

- Page 49 ATmega128 JTAG Interface and If the On-chip debug system is enabled by the OCDEN Fuse and the chip enter Power down or On-chip Debug Power save sleep mode, the main clock source remains enabled. In these sleep modes, this will System contribute significantly to the total current consumption.

- Page 50 CKSEL fuses. The different selec- tions for the delay period are presented in “Clock Sources” on page Reset Sources The ATmega128 has five sources of reset: • Power-on Reset. The MCU is reset when the supply voltage is below the Power-on Reset threshold (V •...

- Page 51 ATmega128 Figure 22. Reset Logic DATA BUS MCU Control and Status Register (MCUCSR) Pull-up Resistor Power-On Reset Circuit Brown-Out BODEN Reset Circuit BODLEVEL Pull-up Resistor SPIKE Reset Circuit RESET FILTER JTAG Reset Watchdog Register Timer Watchdog Oscillator Delay Counters Clock...

- Page 52 Brown-out Reset will occur before V drops to a voltage where correct operation of the microcontroller is no longer guaranteed. The test is performed using BODLEVEL=1for ATmega128L and BODLEVEL=0 for ATmega128. BODLEVEL=1 is not applicable forATmega128 Power-on Reset A Power-on Reset (POR) pulse is generated by an On-chip detection circuit.

- Page 53 Figure 25. External Reset During Operation Brown-out Detection ATmega128 has an On-chip Brown-out Detection (BOD) circuit for monitoring the V level dur- ing operation by comparing it to a fixed trigger level. The trigger level for the BOD can be selected by the fuse BODLEVEL to be 2.7V (BODLEVEL unprogrammed), or 4.0V (BODLEVEL...

- Page 54 Internal Voltage ATmega128 features an internal bandgap reference. This reference is used for Brown-out Detection, and it can be used as an input to the Analog Comparator or the ADC. The 2.56V ref- Reference erence to the ADC is generated from the internal bandgap reference.

- Page 55 Eight different clock cycle periods can be selected to determine the reset period. If the reset period expires without another Watchdog Reset, the ATmega128 resets and executes from the Reset Vector. For timing details on the Watchdog Reset, refer to...

- Page 56 Initial Value • Bits 7..5 – Res: Reserved Bits These bits are reserved bits in the ATmega128 and will always read as zero. • Bit 4 – WDCE: Watchdog Change Enable This bit must be set when the WDE bit is written to logic zero. Otherwise, the Watchdog will not be disabled.

- Page 57 ATmega128 1. In the same operation, write a logic one to WDCE and WDE. A logic one must be written to WDE even though it is set to one before the disable operation starts. 2. Within the next four clock cycles, write a logic 0 to WDE. This disables the Watchdog.

- Page 58 In this mode, the Watchdog Timer is always enabled, and the WDE bit will always read as one. A timed sequence is needed when changing the Watchdog Time-out period. To change the Watchdog Time-out, the following procedure must be followed: ATmega128 2467S–AVR–07/09...

- Page 59 ATmega128 1. In the same operation, write a logical one to WDCE and WDE. Even though the WDE always is set, the WDE must be written to one to start the timed sequence. 2. Within the next four clock cycles, in the same operation, write the WDP bits as desired, but with the WDCE bit cleared.

- Page 60 Interrupts This section describes the specifics of the interrupt handling as performed in ATmega128. For a general explanation of the AVR interrupt handling, refer to “Reset and Interrupt Handling” on page Interrupt Vectors in ATmega128 Table 23. Reset and Interrupt Vectors...

- Page 61 ATmega128 Table 23. Reset and Interrupt Vectors (Continued) Vector Program Address Source Interrupt Definition $003C USART1, RX USART1, Rx Complete $003E USART1, UDRE USART1 Data Register Empty $0040 USART1, TX USART1, Tx Complete $0042 Two-wire Serial Interface $0044 SPM READY...

- Page 62 The most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega128 is: Address LabelsCode Comments $0000 RESET ; Reset Handler $0002 EXT_INT0 ; IRQ0 Handler $0004 EXT_INT1 ; IRQ1 Handler $0006 EXT_INT2 ; IRQ2 Handler...

- Page 63 ATmega128 When the BOOTRST fuse is unprogrammed, the Boot section size set to 8K bytes and the IVSEL bit in the MCUCR Register is set before any interrupts are enabled, the most typical and general program setup for the Reset and Interrupt Vector Addresses is:...

- Page 64 Application section and Boot Lock bit BLB12 is programed, interrupts are disabled while executing from the Boot Loader section. Refer to the section “Boot Loader Support – Read-While- Write Self-Programming” on page 273 for details on Boot Lock bits. ATmega128 2467S–AVR–07/09...

- Page 65 ATmega128 • Bit 0 – IVCE: Interrupt Vector Change Enable The IVCE bit must be written to logic one to enable change of the IVSEL bit. IVCE is cleared by hardware four cycles after it is written or when IVSEL is written. Setting the IVCE bit will disable interrupts, as explained in the IVSEL description above.

- Page 66 71. Refer to the individual module sections for a full description of the alter- nate functions. Note that enabling the alternate function of some of the port pins does not affect the use of the other pins in the port as General Digital I/O. ATmega128 2467S–AVR–07/09...

- Page 67 ATmega128 Ports as General The ports are bi-directional I/O ports with optional internal pull-ups. Figure 30 shows a functional Digital I/O description of one I/O port pin, here generically called Pxn. Figure 30. General Digital I/O DDxn RESET PORTxn RESET...

- Page 68 Consider the clock period starting shortly after the first falling edge of the system clock. The latch is closed when the clock is low, and goes transparent when the clock is high, as indicated by the ATmega128 2467S–AVR–07/09...

- Page 69 ATmega128 shaded region of the “SYNC LATCH” signal. The signal value is latched when the system clock goes low. It is clocked into the PINxn Register at the succeeding positive clock edge. As indi- cated by the two arrows t...

- Page 70 “Interrupt on Rising Edge, Falling Edge, or Any Logic Change on Pin” while the external interrupt is not enabled, the corresponding External Interrupt Flag will be set when resuming from the above mentioned sleep modes, as the clamping in these sleep modes produces the requested logic change. ATmega128 2467S–AVR–07/09...

- Page 71 ATmega128 Unconnected pins If some pins are unused, it is recommended to ensure that these pins have a defined level. Even though most of the digital inputs are disabled in the deep sleep modes as described above, float- ing inputs should be avoided to reduce current consumption in all other modes where the digital inputs are enabled (Reset, Active mode and Idle mode).

- Page 72 The signal is connected directly to the pad, and can be used bi-directionally. The following subsections shortly describes the alternate functions for each port, and relates the overriding signals to the alternate function. Refer to the alternate function description for further details. ATmega128 2467S–AVR–07/09...

- Page 73 ATmega128 Special Function IO Register – SFIOR – – – ACME PSR0 PSR321 SFIOR Read/Write Initial Value • Bit 2 – PUD: Pull-up disable When this bit is written to one, the pull-ups in the I/O ports are disabled even if the DDxn and PORTxn Registers are configured to enable the pull-ups ({DDxn, PORTxn} = 0b01).

- Page 74 OC1C, Output Compare Match C output: The PB7 pin can serve as an external output for the Timer/Counter1 Output Compare C. The pin has to be configured as an output (DDB7 set (one)) to serve this function. The OC1C pin is also the output pin for the PWM mode timer function. ATmega128 2467S–AVR–07/09...

- Page 75 ATmega128 • OC1B, Bit 6 OC1B, Output Compare Match B output: The PB6 pin can serve as an external output for the Timer/Counter1 Output Compare B. The pin has to be configured as an output (DDB6 set (one)) to serve this function. The OC1B pin is also the output pin for the PWM mode timer function.

- Page 76 SPE • MSTR DDOV PVOE SPE • MSTR SPE • MSTR SPE • MSTR PVOV SPI SLAVE OUTPUT SPI MSTR OUTPUT SCK OUTPUT DIEOE DIEOV SPI MSTR INPUT SPI SLAVE INPUT SCK INPUT SPI SS – – – – ATmega128 2467S–AVR–07/09...

- Page 77 ATmega128 Alternate Functions of In ATmega103 compatibility mode, Port C is output only. The ATmega128 is by default shipped Port C in compatibility mode. Thus, if the parts are not programmed before they are put on the PCB, PORTC will be output during first power up, and until the ATmega103 compatibility mode is dis- abled.

- Page 78 • XCK1 – Port D, Bit 5 XCK1, USART1 External clock. The Data Direction Register (DDD4) controls whether the clock is output (DDD4 set) or input (DDD4 cleared). The XCK1 pin is active only when the USART1 operates in Synchronous mode. ATmega128 2467S–AVR–07/09...

- Page 79 ATmega128 • ICP1 – Port D, Bit 4 ICP1 – Input Capture Pin1: The PD4 pin can act as an Input Capture Pin for Timer/Counter1. • INT3/TXD1 – Port D, Bit 3 INT3, External Interrupt source 3: The PD3 pin can serve as an external interrupt source to the MCU.

- Page 80 1. When enabled, the Two-wire Serial Interface enables Slew-Rate controls on the output pins PD0 and PD1. This is not shown in this table. In addition, spike filters are connected between the AIO outputs shown in the port figure and the digital logic of the TWI module. ATmega128 2467S–AVR–07/09...

- Page 81 ATmega128 Alternate Functions of The Port E pins with alternate functions are shown in Table Port E Table 39. Port E Pins Alternate Functions Port Pin Alternate Function INT7/ICP3 (External Interrupt 7 Input or Timer/Counter3 Input Capture Pin) INT6/ T3...

- Page 82 Synchronous mode. • PDO/TXD0 – Port E, Bit 1 PDO, SPI Serial Programming Data Output. During Serial Program Downloading, this pin is used as data output line for the ATmega128. TXD0, UART0 Transmit pin. • PDI/RXD0 – Port E, Bit 0 PDI, SPI Serial Programming Data Input.

- Page 83 ATmega128 Table 41. Overriding Signals for Alternate Functions in PE3..PE0 Signal Name PE3/AIN1/OC3A PE2/AIN0/XCK0 PE1/PDO/TXD0 PE0/PDI/RXD0 PUOE TXEN0 RXEN0 PUOV PORTE0 • PUD DDOE TXEN0 RXEN0 DDOV PVOE OC3B ENABLE UMSEL0 TXEN0 PVOV OC3B XCK0 OUTPUT TXD0 DIEOE DIEOV XCK0 INPUT –...

- Page 84 TCK/ADC4 INPUT INPUT Table 44. Overriding Signals for Alternate Functions in PF3..PF0 Signal Name PF3/ADC3 PF2/ADC2 PF1/ADC1 PF0/ADC0 PUOE PUOV DDOE DDOV PVOE PVOV DIEOE DIEOV – – – – ADC3 INPUT ADC2 INPUT ADC1 INPUT ADC0 INPUT ATmega128 2467S–AVR–07/09...

- Page 85 ATmega128 Alternate Functions of In ATmega103 compatibility mode, only the alternate functions are the defaults for Port G, and Port G Port G cannot be used as General Digital Port Pins. The alternate pin configuration is as follows: Table 45. Port G Pins Alternate Functions...

- Page 86 Table 47. Overriding Signals for Alternate Functions in PG0 Signal Name PG0/WR PUOE PUOV DDOE DDOV PVOE PVOV DIEOE DIEOV – – ATmega128 2467S–AVR–07/09...

- Page 87 ATmega128 Register Description for I/O Ports Port A Data Register – PORTA PORTA7 PORTA6 PORTA5 PORTA4 PORTA3 PORTA2 PORTA1 PORTA0 PORTA Read/Write Initial Value Port A Data Direction Register – DDRA DDA7 DDA6 DDA5 DDA4 DDA3 DDA2 DDA1 DDA0 DDRA...

- Page 88 Initial Value Port E Input Pins Address – PINE PINE7 PINE6 PINE5 PINE4 PINE3 PINE2 PINE1 PINE0 PINF Read/Write Initial Value Port F Data Register – PORTF PORTF7 PORTF6 PORTF5 PORTF4 PORTF3 PORTF2 PORTF1 PORTF0 PORTF Read/Write Initial Value ATmega128 2467S–AVR–07/09...

- Page 89 ATmega128 Port F Data Direction Register – DDRF DDF7 DDF6 DDF5 DDF4 DDF3 DDF2 DDF1 DDF0 DDRF Read/Write Initial Value Port F Input Pins Address – PINF PINF7 PINF6 PINF5 PINF4 PINF3 PINF2 PINF1 PINF0 PINF Read/Write Initial Value Note that PORTF and DDRF Registers are not available in ATmega103 compatibility mode where Port F serves as digital input only.

- Page 90 Therefore, it is recommended to first disable INTn by clearing its Interrupt Enable bit in the EIMSK Register. Then, the ISCn bit can be changed. Finally, the INTn interrupt flag should be cleared by writing a logical one to its Interrupt Flag bit (INTFn) in the EIFR Register before the interrupt is re-enabled. ATmega128 2467S–AVR–07/09...

- Page 91 ATmega128 Table 48. Interrupt Sense Control ISCn1 ISCn0 Description The low level of INTn generates an interrupt request. Reserved The falling edge of INTn generates asynchronously an interrupt request. The rising edge of INTn generates asynchronously an interrupt request. Note: 1.

- Page 92 INT3:0 interrupts disabled, the input buffers on these pins will be disabled. This may cause a logic change in internal signals which will set the INTF3:0 flags. See “Digital Input Enable and Sleep Modes” on page 70 for more information. ATmega128 2467S–AVR–07/09...

- Page 93 ATmega128 8-bit Timer/Counter0 is a general purpose, single channel, 8-bit Timer/Counter module. The main features are: Timer/Counter0 • Single Channel Counter with PWM and • Clear Timer on Compare Match (Auto Reload) • Glitch-free, Phase Correct Pulse Width Modulator (PWM) Asynchronous •...

- Page 94 The main part of the 8-bit Timer/Counter is the programmable bi-directional counter unit. Figure shows a block diagram of the counter and its surrounding environment. Figure 35. Counter Unit Block Diagram DATA BUS TOVn (Int.Req.) TOSC1 count clear Oscillator TCNTn Control Logic Prescaler direction TOSC2 bottom ATmega128 2467S–AVR–07/09...

- Page 95 ATmega128 Signal description (internal signals): count Increment or decrement TCNT0 by 1. direction Selects between increment and decrement. clear Clear TCNT0 (set all bits to zero). Timer/Counter clock. Signalizes that TCNT0 has reached maximum value. bottom Signalizes that TCNT0 has reached minimum value (zero).

- Page 96 Similarly, do not write the TCNT0 value equal to BOTTOM when the counter is downcounting. The setup of the OC0 should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC0 value is to use the force output compare ATmega128 2467S–AVR–07/09...

- Page 97 ATmega128 (FOC0) strobe bit in normal mode. The OC0 Register keeps its value even when changing between waveform generation modes. Be aware that the COM01:0 bits are not double buffered together with the compare value. Changing the COM01:0 bits will take effect immediately.

- Page 98 TOP value. However, changing the TOP to a value close to BOTTOM when the counter is run- ning with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature. If the new value written to OCR0 is lower than the current ATmega128 2467S–AVR–07/09...

- Page 99 ATmega128 value of TCNT0, the counter will miss the compare match. The counter will then have to count to its maximum value (0xFF) and wrap around starting at 0x00 before the compare match can occur. For generating a waveform output in CTC mode, the OC0 output can be set to toggle its logical level on each compare match by setting the Compare Output mode bits to Toggle mode (COM01:0 = 1).

- Page 100 /2 when OCR0 is set to zero. This fea- clk_I/O ture is similar to the OC0 toggle in CTC mode, except the double buffer feature of the output compare unit is enabled in the fast PWM mode. ATmega128 2467S–AVR–07/09...

- Page 101 ATmega128 Phase Correct PWM The phase correct PWM mode (WGM01:0 = 1) provides a high resolution phase correct PWM Mode waveform generation option. The phase correct PWM mode is based on a dual-slope operation. The counter counts repeatedly from BOTTOM to MAX and then from MAX to BOTTOM. In non-...

- Page 102 MAX value in all modes other than phase correct PWM mode. Figure 41. Timer/Counter Timing Diagram, No Prescaling (clk TCNTn MAX - 1 BOTTOM BOTTOM + 1 TOVn Figure 42 shows the same timing data, but with the prescaler enabled. ATmega128 2467S–AVR–07/09...

- Page 103 ATmega128 Figure 42. Timer/Counter Timing Diagram, with Prescaler (f clk_I/O (clk TCNTn MAX - 1 BOTTOM BOTTOM + 1 TOVn Figure 43 shows the setting of OCF0 in all modes except CTC mode. Figure 43. Timer/Counter Timing Diagram, Setting of OCF0, with Prescaler (f...

- Page 104 Modes of operation supported by the Timer/Counter unit are: Normal mode, Clear Timer on Compare match (CTC) mode, and two types of Pulse Width Modulation (PWM) modes. See Table 52 “Modes of Operation” on page ATmega128 2467S–AVR–07/09...

- Page 105 ATmega128 Table 52. Waveform Generation Mode Bit Description WGM01 WGM00 Timer/Counter Update of TOV0 Flag Mode (CTC0) (PWM0) Mode of Operation OCR0 at Set on Normal 0xFF Immediate PWM, Phase 0xFF BOTTOM Correct OCR0 Immediate Fast PWM 0xFF BOTTOM Note: 1.

- Page 106 The Output Compare Register contains an 8-bit value that is continuously compared with the counter value (TCNT0). A match can be used to generate an output compare interrupt, or to generate a waveform output on the OC0 pin. ATmega128 2467S–AVR–07/09...

- Page 107 ATmega128 Asynchronous Operation of the Timer/Counter Asynchronous Status Register – ASSR – – – – TCN0UB OCR0UB TCR0UB ASSR Read/Write Initial Value • Bit 3 – AS0: Asynchronous Timer/Counter0 When AS0 is written to zero, Timer/Counter0 is clocked from the I/O clock, clk .

- Page 108 The recommended procedure for reading TCNT0 is thus as follows: 1. Write any value to either of the registers OCR0 or TCCR0. 2. Wait for the corresponding Update Busy Flag to be cleared. 3. Read TCNT0. ATmega128 2467S–AVR–07/09...

- Page 109 ATmega128 • During asynchronous operation, the synchronization of the interrupt flags for the asynchronous timer takes three processor cycles plus one timer cycle. The timer is therefore advanced by at least one before the processor can read the timer value causing the setting of the interrupt flag.

- Page 110 Timer/Counters are halted and can be configured to the same value without the risk of one of them advancing during configuration. When the TSM bit is written to zero, the PSR0 and PSR321 bits are cleared by hardware, and the Timer/Counters start counting simultaneously. ATmega128 2467S–AVR–07/09...

- Page 111 ATmega128 • Bit 1 – PSR0: Prescaler Reset Timer/Counter0 When this bit is one, the Timer/Counter0 prescaler will be reset. This bit is normally cleared immediately by hardware. If this bit is written when Timer/Counter0 is operating in asynchronous mode, the bit will remain one until the prescaler has been reset. The bit will not be cleared by hardware if the TSM bit is set.

- Page 112 “Pin Configurations” on page 2. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit loca- tions are listed in the “16-bit Timer/Counter Register Description” on page 133. ATmega128 2467S–AVR–07/09...

- Page 113 ATmega128 Figure 46. 16-bit Timer/Counter Block Diagram Count TOVx (Int.Req.) Clear Control Logic Clock Select Direction TCLK Edge Detector BOTTOM ( From Prescaler ) Timer/Counter TCNTx OCFxA (Int.Req.) Waveform OCxA Generation OCRxA OCFxB Fixed (Int.Req.) Values Waveform OCxB Generation OCRxB OCFxC (Int.Req.)

- Page 114 FOCnA, FOCnB, and FOCnC are added in the new TCCRnC Register. • WGMn3 is added to TCCRnB. Interrupt flag and mask bits for output compare unit C are added. The 16-bit Timer/Counter has improvements that will affect the compatibility in some special cases. ATmega128 2467S–AVR–07/09...

- Page 115 ATmega128 Accessing 16-bit The TCNTn, OCRnA/B/C, and ICRn are 16-bit registers that can be accessed by the AVR CPU Registers via the 8-bit data bus. The 16-bit register must be byte accessed using two read or write opera- tions. Each 16-bit timer has a single 8-bit register for temporary storing of the high byte of the 16- bit access.

- Page 116 /* Read TCNTn into i */ i = TCNTn; /* Restore global interrupt flag */ SREG = sreg; return i; Note: 1. See “About Code Examples” on page 9. The assembly code example returns the TCNTn value in the r17:r16 register pair. ATmega128 2467S–AVR–07/09...

- Page 117 ATmega128 The following code examples show how to do an atomic write of the TCNTn Register contents. Writing any of the OCRnA/B/C or ICRn Registers can be done by using the same principle. Assembly Code Example TIM16_WriteTCNTn: ; Save global interrupt flag in r18,SREG ;...

- Page 118 The counting sequence is determined by the setting of the Waveform Generation mode bits (WGMn3:0) located in the Timer/Counter Control Registers A and B (TCCRnA and TCCRnB). There are close connections between how the counter behaves (counts) and how waveforms ATmega128 2467S–AVR–07/09...

- Page 119 ATmega128 are generated on the output compare outputs OCnx. For more details about advanced counting sequences and waveform generation, see “Modes of Operation” on page 124. The Timer/Counter Overflow (TOVn) flag is set according to the mode of operation selected by the WGMn3:0 bits.

- Page 120 Register has been read. After a change of the edge, the Input Capture flag (ICFn) must be cleared by software (writing a logical one to the I/O bit location). For measuring frequency only, the clearing of the ICFn flag is not required (if an interrupt handler is used). ATmega128 2467S–AVR–07/09...

- Page 121 ATmega128 Output Compare The 16-bit comparator continuously compares TCNTn with the Output Compare Register Units (OCRnx). If TCNT equals OCRnx the comparator signals a match. A match will set the Output Compare Flag (OCFnx) at the next timer clock cycle. If enabled (OCIEnx = 1), the output com- pare flag generates an output compare interrupt.

- Page 122 (FOCnx) strobe bits in normal mode. The OCnx Register keeps its value even when changing between waveform generation modes. Be aware that the COMnx1:0 bits are not double buffered together with the compare value. Changing the COMnx1:0 bits will take effect immediately. ATmega128 2467S–AVR–07/09...

- Page 123 ATmega128 Compare Match The Compare Output mode (COMnx1:0) bits have two functions. The waveform generator uses Output Unit the COMnx1:0 bits for defining the output compare (OCnx) state at the next compare match. Secondly the COMnx1:0 bits control the OCnx pin output source.

- Page 124 OCRnA or ICRn, and then counter (TCNTn) is cleared. Figure 51. CTC Mode, Timing Diagram OCnA Interrupt Flag Set or ICFn Interrupt Flag Set (Interrupt on TOP) TCNTn OCnA (COMnA1:0 = 1) (Toggle) Period ATmega128 2467S–AVR–07/09...

- Page 125 ATmega128 An interrupt can be generated at each time the counter value reaches the TOP value by either using the OCFnA or ICFn flag according to the register used to define the TOP value. If the inter- rupt is enabled, the interrupt handler routine can be used for updating the TOP value. However,...

- Page 126 (DDR_OCnx). The PWM waveform is generated by setting (or clearing) the OCnx Register at the compare match between OCRnx and TCNTn, and clearing (or setting) the OCnx Register at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM). ATmega128 2467S–AVR–07/09...

- Page 127 ATmega128 The PWM frequency for the output can be calculated by the following equation: clk_I/O ---------------------------------- - OCnxPWM ⋅ The N variable represents the prescaler divider (1, 8, 64, 256, or 1024). The extreme values for the OCRnx Register represents special cases when generating a PWM waveform output in the fast PWM mode.

- Page 128 (DDR_OCnx). The PWM waveform is generated by setting (or clearing) the OCnx Regis- ter at the compare match between OCRnx and TCNTn when the counter increments, and clearing (or setting) the OCnx Register at compare match between OCRnx and TCNTn when ATmega128 2467S–AVR–07/09...

- Page 129 ATmega128 the counter decrements. The PWM frequency for the output when using phase correct PWM can be calculated by the following equation: clk_I/O --------------------------- - OCnxPCPWM ⋅ ⋅ 2 N TOP The N variable represents the prescaler divider (1, 8, 64, 256, or 1024).

- Page 130 TCNTn when the counter decrements. The PWM frequency for the output when using phase and frequency correct PWM can be calculated by the following equation: clk_I/O --------------------------- - OCnxPFCPWM ⋅ ⋅ 2 N TOP The N variable represents the prescaler divider (1, 8, 64, 256, or 1024). ATmega128 2467S–AVR–07/09...

- Page 131 ATmega128 The extreme values for the OCRnx Register represent special cases when generating a PWM waveform output in the phase correct PWM mode. If the OCRnx is set equal to BOTTOM the output will be continuously low and if set equal to TOP the output will be set to high for non- inverted PWM mode.

- Page 132 BOTTOM + 1 (CTC and FPWM) TCNTn TOP - 1 TOP - 1 TOP - 2 (PC and PFC PWM) TOVn (FPWM) and ICFn (if used as TOP) OCRnx Old OCRnx Value New OCRnx Value (Update at TOP) ATmega128 2467S–AVR–07/09...

- Page 133 ATmega128 16-bit Timer/Counter Register Description Timer/Counter1 Control Register A – TCCR1A COM1A1 COM1A0 COM1B1 COM1B0 COM1C1 COM1C0 WGM11 WGM10 TCCR1A Read/Write Initial Value Timer/Counter3 Control Register A – TCCR3A COM3A1 COM3A0 COM3B1 COM3B0 COM3C1 COM3C0 WGM31 WGM30 TCCR3A Read/Write Initial Value •...

- Page 134 OCnA/OCnB/OCnC on compare match when downcounting. Set OCnA/OCnB/OCnC on compare match when up-counting. Clear OCnA/OCnB/OCnC on compare match when downcounting. Note: special case occurs when OCRnA/OCRnB/OCRnC equals COMnA1/COMnB1//COMnC1 is set. See “Phase Correct PWM Mode” on page 127. for more details. ATmega128 2467S–AVR–07/09...

- Page 135 ATmega128 • Bit 1:0 – WGMn1:0: Waveform Generation Mode Combined with the WGMn3:2 bits found in the TCCRnB Register, these bits control the counting sequence of the counter, the source for maximum (TOP) counter value, and what type of wave-...

- Page 136 TCCRnB is written. • Bit 4:3 – WGMn3:2: Waveform Generation Mode See TCCRnA Register description. • Bit 2:0 – CSn2:0: Clock Select The three clock select bits select the clock source to be used by the Timer/Counter, see Figure Figure ATmega128 2467S–AVR–07/09...

- Page 137 ATmega128 Table 62. Clock Select Bit Description CSn2 CSn1 CSn0 Description No clock source. (Timer/Counter stopped) /1 (No prescaling /8 (From prescaler) /64 (From prescaler) /256 (From prescaler) /1024 (From prescaler) External clock source on Tn pin. Clock on falling edge External clock source on Tn pin.

- Page 138 OCR1BH OCR1B[7:0] OCR1BL Read/Write Initial Value Output Compare Register 1 C – OCR1CH and OCR1CL OCR1C[15:8] OCR1CH OCR1C[7:0] OCR1CL Read/Write Initial Value Output Compare Register 3 A – OCR3AH and OCR3AL OCR3A[15:8] OCR3AH OCR3A[7:0] OCR3AL Read/Write Initial Value ATmega128 2467S–AVR–07/09...

- Page 139 ATmega128 Output Compare Register 3 B – OCR3BH and OCR3BL OCR3B[15:8] OCR3BH OCR3B[7:0] OCR3BL Read/Write Initial Value Output Compare Register 3 C – OCR3CH and OCR3CL OCR3C[15:8] OCR3CH OCR3C[7:0] OCR3CL Read/Write Initial Value The Output Compare Registers contain a 16-bit value that is continuously compared with the counter value (TCNTn).

- Page 140 When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the Timer/Counter3 Output Compare B Match Interrupt is enabled. The corresponding interrupt vector (see “Interrupts” on page 60) is executed when the OCF3B flag, located in ETIFR, is set. ATmega128 2467S–AVR–07/09...

- Page 141 ATmega128 • Bit 2 – TOIE3: Timer/Counter3, Overflow Interrupt Enable When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the Timer/Counter3 Overflow Interrupt is enabled. The corresponding interrupt vector (see “Interrupts” on page 60) is executed when the TOV3 flag, located in ETIFR, is set.

- Page 142 Alternatively, OCF3C can be cleared by writing a logic one to its bit location. • Bit 0 – OCF1C: Timer/Counter1, Output Compare C Match Flag This flag is set in the timer clock cycle after the counter (TCNT1) value matches the Output Compare Register C (OCR1C). ATmega128 2467S–AVR–07/09...

- Page 143 ATmega128 Note that a forced output compare (FOC1C) strobe will not set the OCF1C flag. OCF1C is automatically cleared when the Output Compare Match 1 C interrupt vector is exe- cuted. Alternatively, OCF1C can be cleared by writing a logic one to its bit location.

- Page 144 Tn pin to the counter is updated. Enabling and disabling of the clock input must be done when Tn has been stable for at least one system clock cycle, otherwise it is a risk that a false Timer/Counter clock pulse is generated. ATmega128 2467S–AVR–07/09...

- Page 145 ATmega128 Each half period of the external clock applied must be longer than one system clock cycle to ensure correct sampling. The external clock must be guaranteed to have less than half the sys- tem clock frequency (f < f /2) given a 50/50% duty cycle.

- Page 146 T2 pin. The Clock Select logic block controls which clock source and edge the Timer/Counter uses to increment (or decrement) its value. The Timer/Counter is inactive when no clock source is selected. The output from the clock select logic is referred to as the timer clock (clk ATmega128 2467S–AVR–07/09...

- Page 147 ATmega128 The double buffered Output Compare Register (OCR2) is compared with the Timer/Counter value at all times. The result of the compare can be used by the waveform generator to generate a PWM or variable frequency output on the Output Compare Pin (OC2).

- Page 148 OCFn (Int.Req.) bottom Waveform Generator FOCn WGMn1:0 COMn1:0 The OCR2 Register is double buffered when using any of the pulse width modulation (PWM) modes. For the normal and Clear Timer on Compare (CTC) modes of operation, the double buff- ATmega128 2467S–AVR–07/09...

- Page 149 ATmega128 ering is disabled. The double buffering synchronizes the update of the OCR2 Compare Register to either top or bottom of the counting sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free. The OCR2 Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCR2 buffer Register, and if double buffering is disabled the CPU will access the OCR2 directly.

- Page 150 “Timer/Counter Timing Diagrams” on page 155. Normal Mode The simplest mode of operation is the normal mode (WGM21:0 = 0). In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply ATmega128 2467S–AVR–07/09...

- Page 151 ATmega128 overruns when it passes its maximum 8-bit value (TOP = 0xFF) and then restarts from the bot- tom (0x00). In normal operation the Timer/Counter overflow flag ( 2) will be set in the same timer clock cycle as the TCNT2 becomes zero. The 2 flag in this case behaves like a ninth bit, except that it is only set, not cleared.

- Page 152 (or clearing) the OC2 Register at the compare match between OCR2 and TCNT2, and clearing (or setting) the OC2 Register at the timer clock cycle the coun- ter is cleared (changes from MAX to BOTTOM). ATmega128 2467S–AVR–07/09...

- Page 153 ATmega128 The PWM frequency for the output can be calculated by the following equation: clk_I/O ----------------- - OCnPWM ⋅ N 256 The N variable represents the prescale factor (1, 8, 64, 256, or 1024). The extreme values for the OCR2 Register represents special cases when generating a PWM waveform output in the fast PWM mode.

- Page 154 67. When the OCR2A value is MAX the OCn pin value is the same as the result of a down-counting Compare Match. To ensure symmetry around BOTTOM the OCn value at MAX must correspond to the result of an up- counting Compare Match. ATmega128 2467S–AVR–07/09...

- Page 155 ATmega128 • The timer starts counting from a value higher than the one in OCR2A, and for that reason misses the Compare Match and hence the OCn change that would have happened on the way up. Timer/Counter The Timer/Counter is a synchronous design and the timer clock (clk ) is therefore shown as a clock enable signal in the following figures.

- Page 156 OCF2 and the clearing of TCNT2 in CTC mode. Figure 71. Timer/Counter Timing Diagram, Clear Timer on Compare Match Mode, with Pres- caler (f clk_I/O (clk TCNTn TOP - 1 BOTTOM BOTTOM + 1 (CTC) OCRn OCFn ATmega128 2467S–AVR–07/09...

- Page 157 ATmega128 8-bit Timer/Counter Register Description Timer/Counter Control Register – TCCR2 FOC2 WGM20 COM21 COM20 WGM21 CS22 CS21 CS20 TCCR2 Read/Write Initial Value • Bit 7 – FOC2: Force Output Compare The FOC2 bit is only active when the WGM20 bit specifies a non-PWM mode. However, for ensuring compatibility with future devices, this bit must be set to zero when TCCR2 is written when operating in PWM mode.

- Page 158 The three clock select bits select the clock source to be used by the Timer/Counter. Table 68. Clock Select Bit Description CS22 CS21 CS20 Description No clock source (Timer/Counter stopped) /(No prescaling) /8 (From prescaler) /64 (From prescaler) /256 (From prescaler) ATmega128 2467S–AVR–07/09...

- Page 159 ATmega128 Table 68. Clock Select Bit Description CS22 CS21 CS20 Description /1024 (From prescaler) External clock source on T2 pin. Clock on falling edge External clock source on T2 pin. Clock on rising edge If external pin modes are used for the Timer/Counter2, transitions on the T2 pin will clock the counter even if the pin is configured as an output.

- Page 160 When the SREG I-bit, TOIE2 (Timer/Counter2 Overflow Inter- rupt Enable), and TOV2 are set (one), the Timer/Counter2 Overflow interrupt is executed. In PWM mode, this bit is set when Timer/Counter2 changes counting direction at $00. ATmega128 2467S–AVR–07/09...

- Page 161 ATmega128 Output Compare Modulator (OCM1C2) Overview The Output Compare Modulator (OCM) allows generation of waveforms modulated with a carrier frequency. The modulator uses the outputs from the Output Compare Unit C of the 16-bit Timer/Counter1 and the Output Compare Unit of the 8-bit Timer/Counter2. For more details about these Timer/Counters see “16-bit Timer/Counter (Timer/Counter1 and Timer/Counter3)”...

- Page 162 PB7 output when PORTB7 equals zero. The period 2 high time is one cycle longer than the period 3 high time, but the result on the PB7 output is equal in both periods. ATmega128 2467S–AVR–07/09...

- Page 163 ATmega128 Serial The Serial Peripheral Interface (SPI) allows high-speed synchronous data transfer between the ATmega128 and peripheral devices or between several AVR devices. The ATmega128 SPI Peripheral includes the following features: Interface – SPI • Full-duplex, Three-wire Synchronous Data Transfer •...

- Page 164 69. For more details on automatic port overrides, refer to “Alternate Port Functions” on page Table 69. SPI Pin Overrides Direction, Master SPI Direction, Slave SPI MOSI User Defined Input MISO Input User Defined User Defined Input User Defined Input ATmega128 2467S–AVR–07/09...

- Page 165 ATmega128 Note: 1. See “Alternate Functions of Port B” on page 74 for a detailed description of how to define the direction of the user defined SPI pins. The following code examples show how to initialize the SPI as a Master and how to perform a simple transmission.

- Page 166 /* Set MISO output, all others input */ DDR_SPI = (1<<DD_MISO); /* Enable SPI */ SPCR = (1<<SPE); char SPI_SlaveReceive(void) /* Wait for reception complete */ while(!(SPSR & (1<<SPIF))) /* Return data register */ return SPDR; Note: 1. See “About Code Examples” on page 9. ATmega128 2467S–AVR–07/09...

- Page 167 ATmega128 SS Pin Functionality Slave Mode When the SPI is configured as a slave, the Slave Select (SS) pin is always input. When SS is held low, the SPI is activated, and MISO becomes an output if configured so by the user. All other pins are inputs.

- Page 168 These two bits control the SCK rate of the device configured as a master. SPR1 and SPR0 have no effect on the slave. The relationship between SCK and the Oscillator Clock frequency f shown in the following table: Table 72. Relationship Between SCK and the Oscillator Frequency SPI2X SPR1 SPR0 SCK Frequency ATmega128 2467S–AVR–07/09...

- Page 169 When the SPI is configured as Slave, the SPI is only guaranteed to work at f /4 or lower. The SPI interface on the ATmega128 is also used for program memory and EEPROM down- loading or uploading. See page 300 for SPI Serial Programming and verification.

- Page 170 CHANGE 0 MISO PIN MSB first (DORD = 0) Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 LSB first (DORD = 1) Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 ATmega128 2467S–AVR–07/09...

- Page 171 Multi-processor Communication Mode • Double Speed Asynchronous Communication Mode Dual USART The ATmega128 has two USART’s, USART0 and USART1. The functionality for both USART’s is described below. USART0 and USART1 have different I/O registers as shown in “Register Summary” on page 362.

- Page 172 Shift Register and a two level receive buffer (UDR). The receiver supports the same frame formats as the Transmitter, and can detect frame error, data overrun and parity errors. ATmega128 2467S–AVR–07/09...

- Page 173 ATmega128 AVR USART vs. AVR The USART is fully compatible with the AVR UART regarding: UART – Compatibility • Bit locations inside all USART registers • Baud Rate Generation • Transmitter Operation • Transmit Buffer Functionality • Receiver Operation However, the receive buffering has two improvements that will affect the compatibility in some special cases: •...

- Page 174 (reduced from 16 to 8) for data sampling and clock recovery, and therefore a more accurate baud rate setting and system clock are required when this mode is used. For the Transmitter, there are no downsides. ATmega128 2467S–AVR–07/09...

- Page 175 ATmega128 External Clock External clocking is used by the synchronous slave modes of operation. The description in this section refers to Figure 80 for details. External clock input from the XCK pin is sampled by a synchronization register to minimize the chance of meta-stability.

- Page 176 – Parity bit using even parity even Parity bit using odd parity Data bit n of the character If used, the parity bit is located between the last data bit and first stop bit of a serial frame. ATmega128 2467S–AVR–07/09...

- Page 177 ATmega128 USART The USART has to be initialized before any communication can take place. The initialization pro- Initialization cess normally consists of setting the baud rate, setting frame format and enabling the Transmitter or the Receiver depending on the usage. For interrupt driven USART operation, the global interrupt flag should be cleared (and interrupts globally disabled) when doing the initialization.

- Page 178 The function simply waits for the transmit buffer to be empty by checking the UDRE flag, before loading it with new data to be transmitted. If the data register empty interrupt is utilized, the inter- rupt routine writes the data into the buffer. ATmega128 2467S–AVR–07/09...

- Page 179 ATmega128 Sending Frames with If 9-bit characters are used (UCSZ = 7), the ninth bit must be written to the TXB8 bit in UCSRB 9 Data Bit before the low byte of the character is written to UDR. The following code examples show a transmit function that handles 9 bit characters.

- Page 180 When the first stop bit is received, i.e., a complete serial frame is present in the Receive Shift Register, the contents of the Shift Register will be moved into the receive buffer. The receive buffer can then be read by reading the UDR I/O location. ATmega128 2467S–AVR–07/09...

- Page 181 ATmega128 The following code example shows a simple USART receive function based on polling of the Receive Complete (RXC) flag. When using frames with less than eight bits the most significant bits of the data read from the UDR will be masked to zero. The USART has to be initialized before the function can be used.

- Page 182 = UDR; /* If error, return -1 */ if ( status & (1<<FE)|(1<<DOR)|(1<<UPE) ) return -1; /* Filter the 9th bit, then return */ resh = (resh >> 1) & 0x01; return ((resh << 8) | resl); ATmega128 2467S–AVR–07/09...

- Page 183 ATmega128 Note: 1. See “About Code Examples” on page 9.. The receive function example reads all the I/O registers into the register file before any compu- tation is done. This gives an optimal receive buffer utilization since the buffer location read will be free to accept new data as early as possible.

- Page 184 The asynchronous reception operational range depends on the accuracy of the internal baud rate clock, the rate of the incoming frames, and the frame size in number of bits. ATmega128 2467S–AVR–07/09...

- Page 185 ATmega128 Asynchronous Clock The clock recovery logic synchronizes internal clock to the incoming serial frames. Figure 83 Recovery illustrates the sampling process of the start bit of an incoming frame. The sample rate is 16 times the baud rate for normal mode, and 8 times the baud rate for Double Speed mode. The horizon- tal arrows illustrate the synchronization variation due to the sampling process.

- Page 186 Table 75 Table 76 list the maximum receiver baud rate error that can be tolerated. Note that normal speed mode has higher toleration of baud rate variations. ATmega128 2467S–AVR–07/09...

- Page 187 ATmega128 Table 75. Recommended Maximum Receiver Baud Rate Error for Normal Speed Mode (U2X = Max Total Recommended Max # (Data+Parity Bit) Error % Receiver Error % slow fast 93,20 106,67 +6.67/-6.8 ± 3.0 94,12 105,79 +5.79/-5.88 ± 2.5 94,81 105,11 +5.11/-5.19...

- Page 188 Do not use read-modify-write instructions (SBI and CBI) to set or clear the MPCM bit. The MPCM bit shares the same I/O location as the TXC flag and this might accidentally be cleared when using SBI or CBI instructions. ATmega128 2467S–AVR–07/09...

- Page 189 ATmega128 USART Register Description USARTn I/O Data Register – UDRn RXBn[7:0] UDRn (Read) TXBn[7:0] UDRn (Write) Read/Write Initial Value The USARTn Transmit Data Buffer Register and USARTn Receive Data Buffer Registers share the same I/O address referred to as USARTn Data Register or UDRn. The Transmit Data Buffer Register (TXBn) will be the destination for data written to the UDRn Register location.

- Page 190 Writing this bit to one enables the USARTn Receiver. The Receiver will override normal port operation for the RxDn pin when enabled. Disabling the Receiver will flush the receive buffer invalidating the FEn, DORn and UPEn flags. • Bit 3 – TXENn: Transmitter Enable ATmega128 2467S–AVR–07/09...

- Page 191 ATmega128 Writing this bit to one enables the USARTn Transmitter. The Transmitter will override normal port operation for the TxDn pin when enabled. The disabling of the Transmitter (writing TXENn to zero) will not become effective until ongoing and pending transmissions are completed, i.e., when the Transmit Shift Register and transmit buffer register do not contain data to be transmit- ted.

- Page 192 Rising XCKn Edge Falling XCKn Edge Falling XCKn Edge Rising XCKn Edge USART Baud Rate Registers – UBRRnL and UBRRnH – – – – UBRRn[11:8] UBRRnH UBRRn[7:0] UBRRnL Read/Write Initial Value UBRRnH is not available in mega103 compatibility mode ATmega128 2467S–AVR–07/09...

- Page 193 ATmega128 • Bit 15:12 – Reserved Bits These bits are reserved for future use. For compatibility with future devices, these bit must be written to zero when UBRRnH is written. • Bit 11:0 – UBRRn11:0: USARTn Baud Rate Register This is a 12-bit register which contains the USARTn baud rate. The UBRRnH contains the four most significant bits, and the UBRRnL contains the eight least significant bits of the USARTn baud rate.

- Page 194 – – – 0.0% – – – – 250k – – – – – – – – – – 0.0% 62.5 kbps 125 kbps 115.2 kbps 230.4 kbps 125 kbps 250 kbps UBRR = 0, Error = 0.0% ATmega128 2467S–AVR–07/09...

- Page 195 ATmega128 Table 83. Examples of UBRR Settings for Commonly Used Oscillator Frequencies = 3.6864 MHz = 4.0000 MHz = 7.3728 MHz Baud U2X = 0 U2X = 1 U2X = 0 U2X = 1 U2X = 0 U2X = 1...

- Page 196 -7.8% -7.8% 5.3% 0.5M 0.0% 0.0% – – -7.8% -7.8% -7.8% – – 0.0% – – – – -7.8% -7.8% 0.5 Mbps 1 Mbps 691.2 kbps 1.3824 Mbps 921.6 kbps 1.8432 Mbps UBRR = 0, Error = 0.0% ATmega128 2467S–AVR–07/09...

- Page 197 ATmega128 Table 85. Examples of UBRR Settings for Commonly Used Oscillator Frequencies = 16.0000 MHz Baud U2X = 0 U2X = 1 Rate (bps) UBRR Error UBRR Error 2400 -0.1% 0.0% 4800 0.2% -0.1% 9600 0.2% 0.2% 14.4k 0.6% -0.1% 19.2k...

- Page 198 This implements a wired-AND function which is essential to the operation of the interface. A low level on a TWI bus line is generated when one or more TWI devices output a zero. A high level is output when all TWI devices tri-state their outputs, allowing the pull-up resistors to pull the line ATmega128 2467S–AVR–07/09...

- Page 199 ATmega128 high. Note that all AVR devices connected to the TWI bus must be powered in order to allow any bus operation. The number of devices that can be connected to the bus is only limited by the bus capacitance limit of 400 pF and the 7-bit slave address space.

- Page 200 If the receiver leaves the SDA line high, a NACK is signalled. When the receiver has received the last byte, or for some reason cannot receive any more bytes, it should inform the transmitter by sending a NACK after the final byte. The MSB of the data byte is transmitted first. ATmega128 2467S–AVR–07/09...

- Page 201 ATmega128 Figure 90. Data Packet Format Data MSB Data LSB Aggregate SDA from Transmitter SDA from Receiver SCL from Master STOP, REPEATED SLA+R/W Data Byte START or Next Data Byte Combining Address A transmission basically consists of a START condition, a SLA+R/W, one or more data packets and Data Packets Into and a STOP condition.

- Page 202 If several masters are trying to address the same slave, arbitration will continue into the data packet. Figure 93. Arbitration Between two Masters START Master A loses Arbitration, SDA SDA from Master A SDA from Master B SDA Line Synchronized SCL Line ATmega128 2467S–AVR–07/09...

- Page 203 ATmega128 Note that arbitration is not allowed between: • A REPEATED START condition and a data bit • A STOP condition and a data bit • A REPEATED START and a STOP condition It is the user software’s responsibility to ensure that these illegal arbitration conditions never occur.

- Page 204 In addition to the 8-bit TWDR, the Bus Interface Unit also contains a register containing the (N)ACK bit to be transmitted or received. This (N)ACK Regis- ter is not directly accessible by the application software. However, when receiving, it can be set ATmega128 2467S–AVR–07/09...

- Page 205 ATmega128 or cleared by manipulating the TWI Control Register (TWCR). When in Transmitter mode, the value of the received (N)ACK bit can be determined by the value in the TWSR. The START/STOP Controller is responsible for generation and detection of START, REPEATED START, and STOP conditions.

- Page 206 However, if the bus is not free, the TWI waits until a STOP condition is detected, and then generates a new START condition to claim the bus Master status. TWSTA must be cleared by software when the START condition has been transmitted. ATmega128 2467S–AVR–07/09...

- Page 207 ATmega128 • Bit 4 – TWSTO: TWI STOP Condition Bit Writing the TWSTO bit to one in Master mode will generate a STOP condition on the Two-wire Serial Bus. When the STOP condition is executed on the bus, the TWSTO bit is cleared auto- matically.

- Page 208 TWI bus cycle by manipulating the TWCR and TWDR Registers. Figure 95 is a simple example of how the application can interface to the TWI hardware. In this example, a master wishes to transmit a single data byte to a slave. This description is quite ATmega128 2467S–AVR–07/09...

- Page 209 ATmega128 abstract, a more detailed explanation follows later in this section. A simple code example imple- menting the desired behavior is also presented. Figure 95. Interfacing the Application to the TWI in a Typical Transmission 1. Application 3. Check TWSR to see if START 5.

- Page 210 TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the STOP condi- tion. Note that TWINT is NOT set after a STOP condition has been sent. ATmega128 2467S–AVR–07/09...

- Page 211 ATmega128 Even though this example is simple, it shows the principles involved in all TWI transmissions. These can be summarized as follows: • When the TWI has finished an operation and expects application response, the TWINT flag is set. The SCL line is pulled low until TWINT is cleared.

- Page 212 For I/O registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. ATmega128 2467S–AVR–07/09...

- Page 213 ATmega128 Transmission The TWI can operate in one of four major modes. These are named Master Transmitter (MT), Modes Master Receiver (MR), Slave Transmitter (ST) and Slave Receiver (SR). Several of these modes can be used in the same application. As an example, the TWI can use MT mode to write data into a TWI EEPROM, MR mode to read the data back from the EEPROM.

- Page 214 TWCR: TWCR TWINT TWEA TWSTA TWSTO TWWC TWEN – TWIE value A REPEATED START condition is generated by writing the following value to TWCR: TWCR TWINT TWEA TWSTA TWSTO TWWC TWEN – TWIE value ATmega128 2467S–AVR–07/09...

- Page 215 ATmega128 After a repeated START condition (state $10) the Two-wire Serial Interface can access the same slave again, or a new slave without transmitting a STOP condition. Repeated START enables the master to switch between slaves, Master Transmitter mode and Master Receiver mode without losing control of the bus.

- Page 216 DATA From master to slave and their associated acknowledge bits From slave to master This number (contained in TWSR) corresponds to a defined state of the Two-wire Serial Bus. The prescaler bits are zero or masked to zero ATmega128 2467S–AVR–07/09...

- Page 217 ATmega128 Master Receiver Mode In the Master Receiver Mode, a number of data bytes are received from a slave transmitter (see Figure 98). In order to enter a Master mode, a START condition must be transmitted. The format of the following address packet determines whether Master Transmitter or Master Receiver mode is to be entered.

- Page 218 DATA From master to slave and their associated acknowledge bits This number (contained in TWSR) corresponds From slave to master to a defined state of the Two-wire Serial Bus. The prescaler bits are zero or masked to zero ATmega128 2467S–AVR–07/09...

- Page 219 ATmega128 Table 89. Status Codes for Master Receiver Mode Status Code Application Software Response (TWSR) Status of the Two-wire Serial To TWCR Prescaler Bits Bus and Two-wire Serial Inter- To/from TWDR TWINT TWEA are 0 face Hardware Next Action Taken by TWI Hardware...

- Page 220 Note that the Two-wire Serial Interface Data Register – TWDR does not reflect the last byte present on the bus when waking up from these sleep modes. ATmega128 2467S–AVR–07/09...

- Page 221 ATmega128 Table 90. Status Codes for Slave Receiver Mode Status Code Application Software Response (TWSR) Status of the Two-wire Serial Bus To TWCR Prescaler Bits and Two-wire Serial Interface To/from TWDR TWINT TWEA are 0 Hardware Next Action Taken by TWI Hardware Own SLA+W has been received;...

- Page 222 Figure 102. Data Transfer in Slave Transmitter Mode Device 1 Device 2 Device 3 ..Device n SLAVE MASTER TRANSMITTER RECEIVER To initiate the Slave Transmitter mode, TWAR and TWCR must be initialized as follows: ATmega128 2467S–AVR–07/09...

- Page 223 ATmega128 TWAR TWA6 TWA5 TWA4 TWA3 TWA2 TWA1 TWA0 TWGCE value Device’s Own Slave Address The upper seven bits are the address to which the Two-wire Serial Interface will respond when addressed by a master. If the LSB is set, the TWI will respond to the general call address ($00), otherwise it will ignore the general call address.

- Page 224 From slave to master to a defined state of the Two-wire Serial Bus. The prescaler bits are zero or masked to zero Miscellaneous States There are two status codes that do not correspond to a defined TWI state, see Table ATmega128 2467S–AVR–07/09...

- Page 225 ATmega128 Status $F8 indicates that no relevant information is available because the TWINT flag is not set. This occurs between other states, and when the TWI is not involved in a serial transfer. Status $00 indicates that a bus error has occurred during a Two-wire Serial Bus transfer. A bus error occurs when a START or STOP condition occurs at an illegal position in the format frame.

- Page 226 Data byte will be received and NOT ACK will be returned Direction Data byte will be received and ACK will be returned Read Last data byte will be transmitted and NOT ACK should be received Data byte will be transmitted and ACK should be received ATmega128 2467S–AVR–07/09...

- Page 227 ATmega128 Analog The Analog Comparator compares the input values on the positive pin AIN0 and negative pin AIN1. When the voltage on the positive pin AIN0 is higher than the voltage on the negative pin Comparator AIN1, the Analog Comparator Output, ACO, is set. The comparator’s output can be set to trigger the Timer/Counter1 Input Capture function.

- Page 228 If the Analog Comparator Multiplexer Enable bit (ACME in Multiplexed Input SFIOR) is set and the ADC is switched off (ADEN in ADCSRA is zero), MUX2..0 in ADMUX select the input pin to replace the negative input to the Analog Comparator, as shown in Table ATmega128 2467S–AVR–07/09...

- Page 229 ATmega128 94. If ACME is cleared or ADEN is set, AIN1 is applied to the negative input to the Analog Comparator. Table 94. Analog Comparator Multiplexed Input ACME ADEN MUX2..0 Analog Comparator Negative Input AIN1 AIN1 ADC0 ADC1 ADC2 ADC3...

- Page 230 • Sleep Mode Noise Canceler The ATmega128 features a 10-bit successive approximation ADC. The ADC is connected to an 8-channel Analog Multiplexer which allows 8 single-ended voltage inputs constructed from the pins of Port F. The single-ended voltage inputs refer to 0V (GND).

- Page 231 ATmega128 Figure 108. Analog to Digital Converter Block Schematic ADC CONVERSION COMPLETE IRQ 8-BIT DATA BUS ADC MULTIPLEXER ADC CTRL. & STATUS ADC DATA REGISTER SELECT (ADMUX) REGISTER (ADCSRA) (ADCH/ADCL) PRESCALER MUX DECODER CONVERSION LOGIC AVCC INTERNAL 2.56V REFERENCE SAMPLE & HOLD...

- Page 232 Free Running mode is selected by writing the ADFR bit in ADCSRA to one. The first conversion must be started by writing a logical one to the ADSC bit in ADCSRA. In this mode the ADC will perform successive conversions independently of whether the ADC Interrupt Flag, ADIF is cleared or not. ATmega128 2467S–AVR–07/09...

- Page 233 ATmega128 Prescaling and Figure 109. ADC Prescaler Conversion Timing ADEN Reset 7-BIT ADC PRESCALER ADPS0 ADPS1 ADPS2 ADC CLOCK SOURCE By default, the successive approximation circuitry requires an input clock frequency between 50 kHz and 200 kHz to get maximum resolution. If a lower resolution than 10 bits is needed, the input clock frequency to the ADC can be higher than 200 kHz to get a higher sample rate.

- Page 234 MUX and REFS Update Update Figure 112. ADC Timing Diagram, Free Running Conversion One Conversion Next Conversion Cycle Number ADC Clock ADSC ADIF ADCH MSB of Result ADCL LSB of Result Sample & Hold Conversion MUX and REFS Complete Update ATmega128 2467S–AVR–07/09...

- Page 235 ATmega128 Table 95. ADC Conversion Time Sample & Hold (Cycles from Conversion Time Condition Start of Conversion) (Cycles) First conversion 13.5 Normal conversions, single ended Normal conversions, differential 1.5/2.5 13/14 Differential Gain When using differential gain channels, certain aspects of the conversion need to be taken into Channels consideration.

- Page 236 Note that the ADC will not be automatically turned off when entering other sleep modes than Idle mode and ADC Noise Reduction mode. The user is advised to write zero to ADEN before enter- ing such sleep modes to avoid excessive power consumption. If the ADC is enabled in such ATmega128 2467S–AVR–07/09...

- Page 237 ATmega128 sleep modes and the user wants to perform differential conversions, the user is advised to switch the ADC off and on after waking up from sleep to prompt an extended conversion to get a valid result. Analog Input Circuitry The Analog Input circuitry for single ended channels is illustrated in Figure 113.

- Page 238 This offset residue can be then subtracted in software from the measurement results. Using this kind of software based offset correction, offset on any channel can be reduced below one LSB. ATmega128 2467S–AVR–07/09...

- Page 239 ATmega128 ADC Accuracy An n-bit single-ended ADC converts a voltage linearly between GND and V in 2 steps Definitions (LSBs). The lowest code is read as 0, and the highest code is read as 2 Several parameters describe the deviation from the ideal behavior: •...

- Page 240 • Absolute Accuracy: The maximum deviation of an actual (unadjusted) transition compared to an ideal transition for any code. This is the compound effect of offset, gain error, differential error, non-linearity, and quantization error. Ideal value: ±0.5 LSB. ATmega128 2467S–AVR–07/09...

- Page 241 ATmega128 ADC Conversion After the conversion is complete (ADIF is high), the conversion result can be found in the ADC Result Result Registers (ADCL, ADCH). For single ended conversion, the result is ⋅ 1024 -------------------------- where V is the voltage on the selected input pin and V...

- Page 242 The ADLAR bit affects the presentation of the ADC conversion result in the ADC Data Register. Write one to ADLAR to left adjust the result. Otherwise, the result is right adjusted. Changing the ADLAR bit will affect the ADC Data Register immediately, regardless of any ongoing ATmega128 2467S–AVR–07/09...

- Page 243 ATmega128 conversions. For a complete description of this bit, see “The ADC Data Register – ADCL and ADCH” on page 245. • Bits 4:0 – MUX4:0: Analog Channel and Gain Selection Bits The value of these bits selects which combination of analog inputs are connected to the ADC.

- Page 244 When this bit is written to one and the I-bit in SREG is set, the ADC Conversion Complete Inter- rupt is activated. • Bits 2:0 – ADPS2:0: ADC Prescaler Select Bits These bits determine the division factor between the XTAL frequency and the input clock to the ADC. ATmega128 2467S–AVR–07/09...

- Page 245 ATmega128 Table 99. ADC Prescaler Selections ADPS2 ADPS1 ADPS0 Division Factor The ADC Data Register – ADCL and ADCH ADLAR = 0: – – – – – – ADC9 ADC8 ADCH ADC7 ADC6 ADC5 ADC4 ADC3 ADC2 ADC1 ADC0 ADCL...

- Page 246 “IEEE 1149.1 (JTAG) Boundary-scan” on page 252, respectively. The On-chip Debug support is considered being private JTAG instructions, and distributed within ATMEL and to selected third party vendors only. Figure 120 shows a block diagram of the JTAG interface and the On-chip Debug system. The TAP Controller is a state machine controlled by the TCK and TMS signals.

- Page 247 ATmega128 The IEEE std. 1149.1 also specifies an optional TAP signal; TRST – Test ReSeT – which is not provided. When the JTAGEN fuse is unprogrammed, these four TAP pins are normal port pins and the TAP controller is in reset. When programmed and the JTD bit in MCUCSR is cleared, the TAP input signals are internally pulled high and the JTAG is enabled for Boundary-scan and program- ming.

- Page 248 The TMS input must be held low during input of the 3 LSBs in order to remain in the Shift-IR state. The MSB of the instruction is shifted in when this state is left by setting TMS high. While the instruction is shifted in from the TDI pin, the captured IR-state 0x01 is shifted out ATmega128 2467S–AVR–07/09...

- Page 249 ATmega128 on the TDO pin. The JTAG Instruction selects a particular Data Register as path between TDI and TDO and controls the circuitry surrounding the selected Data Register. • Apply the TMS sequence 1, 1, 0 to re-enter the Run-Test/Idle state. The instruction is latched onto the parallel output from the Shift Register path in the Update-IR state.

- Page 250 The AVR Studio enables the user to fully control execution of programs on an AVR device with On-chip Debug capability, AVR In-Circuit Emulator, or the built-in AVR Instruction Set Simulator. AVR Studio supports source level execution of Assembly programs assembled with Atmel Cor- poration’s AVR Assembler and C programs compiled with third party vendors’ compilers.